1)实验目的

(1)熟悉寄存器的电路结构和工作原理。

(2)掌握中规模集成电路74LS194双向移位寄存器的逻辑功能和使用方法。

(3)熟悉移位寄存器的逻辑电路和工作原理。

2)实验原理

在数字电路中,常常需要将一些数码、指令或运算结果暂时存放起来,能完成这种作用的部件叫做寄存器。寄存器具有清除数码、接收数码、存放数码和传送数码的功能。寄存器常分为数码寄存器和移位寄存器两种,其区别在于有无移位的功能。

(1)数码寄存器

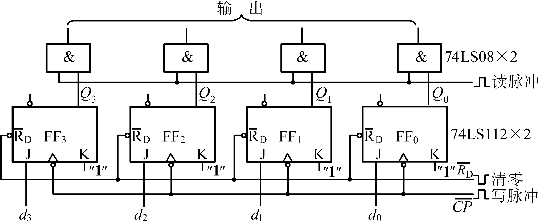

由JK触发器组成的数码寄存器如图4.59所示,![]() 端输入负脉冲时,使各移位寄存器清零。

端输入负脉冲时,使各移位寄存器清零。

CP端的脉冲为写脉冲,当CP脉冲下降沿到来时,d3、d2、d1、d0各位数据被输入到寄存器中,并寄存。数码的输出由读出脉冲控制。所以数据寄存器就有如下特点:①能清除;②能写入;③能寄存;④能读出。这种输入、输出方式称为并行输入、并行输出。

图4.59 4位数码寄存器

(2)移位寄存器

具有移位逻辑功能的寄存器称为移位寄存器。移位功能是每位触发器的输出与下一级触发器的输入相连而形成的。它可以起到多方面的作用,可以存贮或延迟输入—输出信息,也可以用来把串行的二进制数转换为并行的二进制数(串并转换)或者相反(并串转换)。在计算机电路中,还应用移位寄存器来实现二进制的乘2和除2功能。

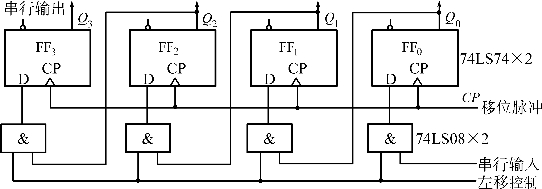

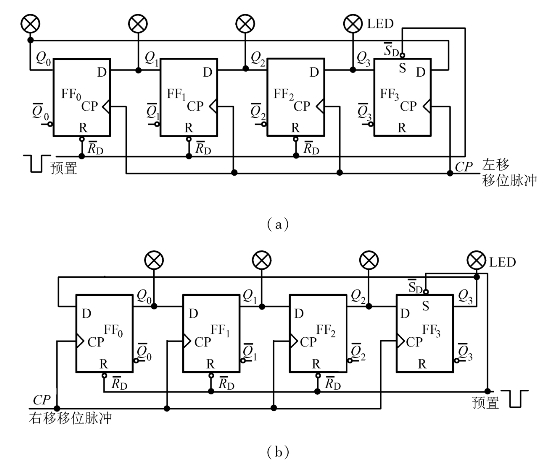

图4.60为4位串行输入、串并行输出的左移移位寄存器(由4个D触发器构成)。

图4.60 4位串行输入、串并行输出的左移移位寄存器

由图4.60可知,CP脉冲的输入(上升沿起作用)作为同步移位脉冲,数据(码)的移位操作由“左移控制”端控制,数码是从串行输入端输入,输出可以是串行输出或并行输出。

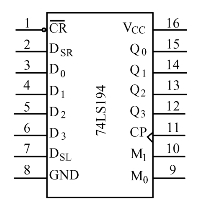

移位寄存器在应用中需要左移、右移、保持、并行输入/输出或串行输入/输出等多种功能。具有上述多种功能的移位寄存器称为多功能双向移位寄存器。如中规模集成电路74LS194就是具有左移、右移、清零、数据并入/并出(串出)等多种功能的移位寄存器。它的管脚排列见图4.61,逻辑功能见表4.26。

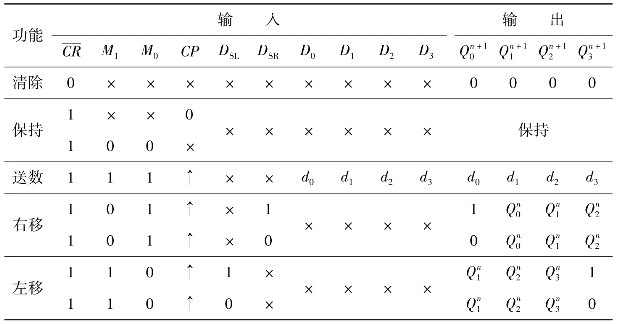

由表4.26可知,74LS194具有如下功能:

①清除:当![]() 时,不管其他输入为何种状态,输出全为0状态。

时,不管其他输入为何种状态,输出全为0状态。

②保持:CP=0,![]() 时,其他输入为任意状态,输出状态保持。或者

时,其他输入为任意状态,输出状态保持。或者![]() ,M1、M0均为0,其他输入为任意状态,输出状态也保持。

,M1、M0均为0,其他输入为任意状态,输出状态也保持。

图4.61 74LS194管脚排列图

③置数(送数):![]() ,M1=M0=1,在CP脉冲上升沿时,将输入端数据D0、D1、D2、D3置入Q0、Q1、Q2、Q3中,并寄存。

,M1=M0=1,在CP脉冲上升沿时,将输入端数据D0、D1、D2、D3置入Q0、Q1、Q2、Q3中,并寄存。

④右移:![]() ,M1=0,M0=1,在CP脉冲上升沿时,实现右移操作,此时若DSR=0,则0向Q0移位,若DSR=1,则1向Q0移位。

,M1=0,M0=1,在CP脉冲上升沿时,实现右移操作,此时若DSR=0,则0向Q0移位,若DSR=1,则1向Q0移位。

⑤左移:![]() ,M1=1,M0=0,在CP脉冲上升沿时,实现左移操作,此时若DSL=0,则0向Q3移位,若DSL=1,则1向Q3移位。

,M1=1,M0=0,在CP脉冲上升沿时,实现左移操作,此时若DSL=0,则0向Q3移位,若DSL=1,则1向Q3移位。

表4.26 74LS194逻辑功能表

(3)移位寄存器的应用

移位寄存器用来构成计数器,这是在实际工程中经常用到的。比如用移位寄存器构成环形计数器、扭环形计数器和自启动扭环形计数器等。它还可用作数据寄存器,比如,两个数相加、相减其结果的存放等。

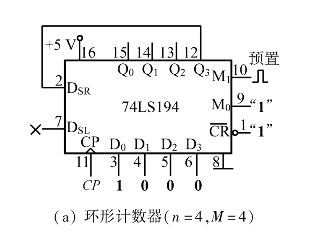

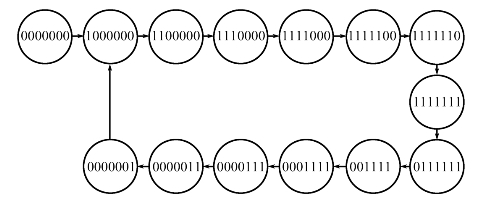

用74LS194构成的环形计数器、扭环形计数器和自启动的扭环形计数器如图4.62所示。

图4.62 74LS194双向移位寄存器的应用

在图4.62(a)中,输入4个移位脉冲,完成一次移位循环,即它是模M=4的环形计数器,如果需要模M=8的环形计数器,则需两片74LS194,这种环形计数器无自启动能力,必须在启动计数操作前,先置某个数在移位寄存器内(如0001或0011)然后再进行循环计数。

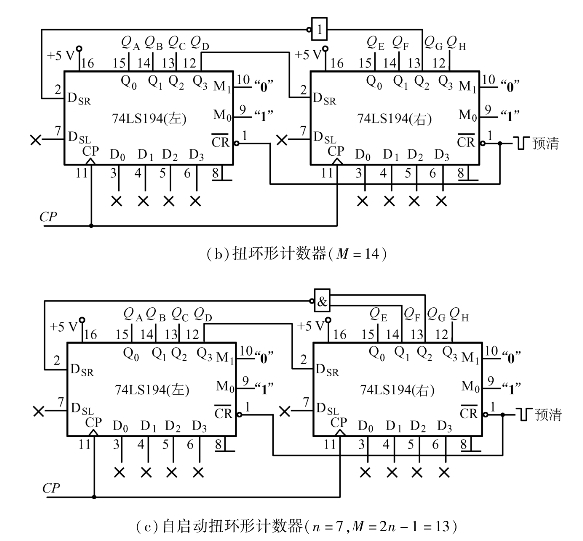

图4.62(b)为两片74LS194组成的扭环形计数器,它比图4.62(a)中的计数范围要大,最大模M=16。而环形计数器两片74LS194最大模M=8。所以,同样的计数范围,图4.62(b)连接方法比图4.62(a)要节省一半电路。扭环形计数器实际上就是把某一位取反后接到数据输入端,进行向左或向右移位。图4.62(b)就是把右边一片74LS194的Q2取反后接到左边一片74LS194的DSR右移输入端,构成模M=14的扭环形计数器。该计数器清零后即可启动,实现扭环形计数。图4.62(c)为两片74LS194构成的M=13的自启动扭环形计数器,其状态表如图4.63所示。

图4.63 74LS194构成的自启动环形计数器,模M=13的状态图

移位寄存器在数字运算电路中,常用作数据的存放、寄存等。

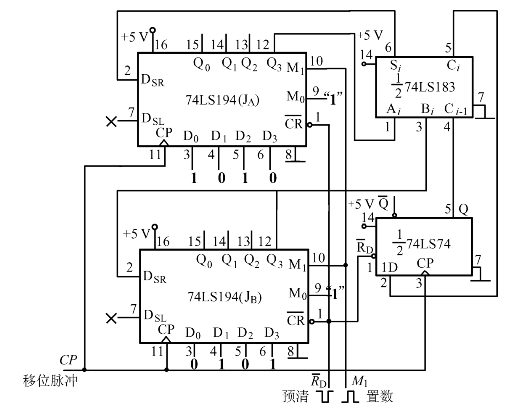

图4.64就是74LS194移位寄存器的具体应用。两个寄存器(JA、JB)分别存放数据A和B,两者通过相加后,再送到寄存器JA中。设JA寄存器存放的数据为1010,JB寄存器存放的数据为0101,即JA=10,JB=5,相加后(JA+JB=15),结果为1111,再送至JA中。

图4.64中,全加器用74LS183,进位触发器用D触发器74LS74。

图4.64 用74LS194双向移位寄存器组成的加法电路JA+JB➝JA(https://www.daowen.com)

3)实验内容

(1)数据寄存器

①在实验系统中,选4只JK触发器(把74LS112双JK触发器芯片自行插入实验系统中),按图4.59直接接线。d3、d2、d1、d0接数据开关或逻辑开关,与门输出接4只LED发光二极管,4只触发器的清零端![]() 连接到实验系统中复位按钮,写入脉冲接单次脉冲,读出脉冲接逻辑开关。

连接到实验系统中复位按钮,写入脉冲接单次脉冲,读出脉冲接逻辑开关。

②接线完毕,则可通电实验。置d3d2d1d0=1010,清“0”()后,按动单次脉冲,这时Q3、Q2、Q1、Q0将被置为1010,再将读出开关(逻辑开关)置1,就可观察到4只发光二极管为亮、灭、亮、灭,即输出数据为1010。

③改变d3、d2、d1、d0的数值,重复步骤②,验证其数据寄存的功能,并记录结果。

用D触发器代替JK触发器,也能很方便地实现,可自行连接实验线路,进行验证。

(2)移位寄存器

①用4只D触发器(74LS74)连成左移、右移移位寄存器,按图4.65(a)连线。D触发器用实验系统中的D触发器(也可自行插入)。

②接线完毕后,先置数据为0001,然后输入移位脉冲。置数,即把Q3、Q2、Q1、Q0置成0001。按动单次脉冲,移位寄存器可实现左移功能。

③按图4.65(b)连线,方法同步骤②,则可完成右移移位功能。

图4.65 D触发器构成移位寄存器的实验线路图

④图4.60为带移位控制的串入、串出、并出的4位左移移位寄存器,可自行连线进行实验论证。

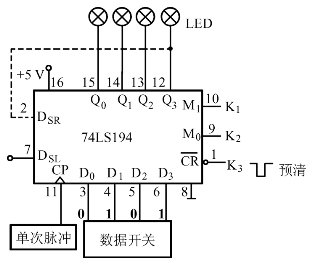

(3)集成移位寄存器

①基本功能验证

图4.66 74LS194双向移位寄存器实验接线图

将74LS194插入实验系统中,按图4.66接线,16脚接电源正极,8脚接地,输出端Q3、Q2、Q1、Q0接4只LED发光二极管,工作方式控制端M1、M0及清零端分别接逻辑开关K1、K2和复位按钮K3(“![]() ”),CP端接单次脉冲,数据输入端D0、D1、D2、D3分别接4只数据开关或逻辑开关。

”),CP端接单次脉冲,数据输入端D0、D1、D2、D3分别接4只数据开关或逻辑开关。

接线完毕后,接通电源,即可进行74LS194双向移位寄存器的功能验证(对照表4.26输入各有关参数)。

清除(零):按复位按钮K3(“![]() ”),使

”),使![]() =0,这时Q0、Q1、Q2、Q3接的4只LED发光二极管全灭,即Q0Q1Q2Q3=0000。

=0,这时Q0、Q1、Q2、Q3接的4只LED发光二极管全灭,即Q0Q1Q2Q3=0000。

保持:使![]() ,CP=0状态,拨动逻辑开关K1(M1)和K2(M0),输出状态不变,或者使

,CP=0状态,拨动逻辑开关K1(M1)和K2(M0),输出状态不变,或者使![]() =1,M1=M0=0,按动单次脉冲,这时输出状态仍不变。

=1,M1=M0=0,按动单次脉冲,这时输出状态仍不变。

置数:使![]() ,M1=M0=1(即K1=K2=1),置数据开关为0101(D0~D3),按动单次脉冲,这时数据0101(D0~D3)已存入Q0~Q3中。LED发光二极管此时为灭、亮、灭、亮(即0101)。变换数据D0~D3=1011,输入单次脉冲,则数据1011在CP上升沿时存入Q0~Q3中。右移:把Q3接到DSR,见图4.66中虚线,按上述方法先置入数据0001(这时使

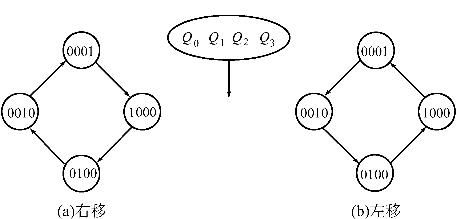

,M1=M0=1(即K1=K2=1),置数据开关为0101(D0~D3),按动单次脉冲,这时数据0101(D0~D3)已存入Q0~Q3中。LED发光二极管此时为灭、亮、灭、亮(即0101)。变换数据D0~D3=1011,输入单次脉冲,则数据1011在CP上升沿时存入Q0~Q3中。右移:把Q3接到DSR,见图4.66中虚线,按上述方法先置入数据0001(这时使![]() ,M1=M0=1,D0~D3=0001)。再置M1=0,M0=1为右移方式,输入单次脉冲,移位寄存器这时在CP上升沿时实现右移操作。按动4次单次脉冲,一次移位循环结束。即如图4.67(a)状态图所示。

,M1=M0=1,D0~D3=0001)。再置M1=0,M0=1为右移方式,输入单次脉冲,移位寄存器这时在CP上升沿时实现右移操作。按动4次单次脉冲,一次移位循环结束。即如图4.67(a)状态图所示。

左移:将Q3连到DSR的线断开,而把Q0接到左移输入DSL端,其余方法同上述右移。即![]() ,M0=0,M1=1(寄存器起始状态仍为0001),则输入4个移位脉冲后,数据左移,最后结果仍为0001。其左移状态图见图4.67(b)。

,M0=0,M1=1(寄存器起始状态仍为0001),则输入4个移位脉冲后,数据左移,最后结果仍为0001。其左移状态图见图4.67(b)。

图4.67 74LS194右移、左移状态图

再把Q3接到DSL(Q0与DSL连线断开),输入单次脉冲,观察移位情况,记录并分析。

②应用

用74LS194移位寄存器可构成各种计数器。

a.按图4.62(a)接线,Q0~Q3接4只LED发光二极管,DSR与Q3相连,D0~D3接数据开关(或逻辑开关),M1、M0、![]() 分别接逻辑开关和复位开关,CP接单次脉冲,电源+、-分别接芯片16、8脚。接线完毕,预置寄存器为1000状态,并使M0=1,M1=0,

分别接逻辑开关和复位开关,CP接单次脉冲,电源+、-分别接芯片16、8脚。接线完毕,预置寄存器为1000状态,并使M0=1,M1=0,![]() ,寄存器处于移位(右移)状态,即环形计数状态。输入单次计数脉冲,观察LED发光二极管Q0~Q3的状态,不难发现Q0~Q3按右移方式出现,且一次循环为4个脉冲,即计数器的模M=4。

,寄存器处于移位(右移)状态,即环形计数状态。输入单次计数脉冲,观察LED发光二极管Q0~Q3的状态,不难发现Q0~Q3按右移方式出现,且一次循环为4个脉冲,即计数器的模M=4。

b.按图4.62(b)接线,并按步骤a.进行实验,发现QA~QG输出按右移方式出现,且一次循环为14个脉冲,即计数器的模为14(M=14)。这种计数器称为扭环形计数器。

c.按图4.62(c)接线,进行实验论证。计数器的状态应和图4.63所示的M=13的状态图一致。

d.按图4.64接线,进行JA+JB➝JA。

这里CP接单次脉冲,![]() 接复位开关,M1、M0接逻辑开关,JA的D0~D3和JB的D0~D3分别接数据开关。寄存器JA送全加器(74LS183)的Ai端,JB送全加器(74LS183)的Bi端,全加器的进位Ci由D触发器(74LS74)寄存,D触发器的输出作为上次进位的输出接到全加器的Ci-1端,全加器的和Si接到寄存器JA的输入端,这里选用右移方式,则把和Si接到右移输入端DSR,JB寄存器数据仍送回JB中。

接复位开关,M1、M0接逻辑开关,JA的D0~D3和JB的D0~D3分别接数据开关。寄存器JA送全加器(74LS183)的Ai端,JB送全加器(74LS183)的Bi端,全加器的进位Ci由D触发器(74LS74)寄存,D触发器的输出作为上次进位的输出接到全加器的Ci-1端,全加器的和Si接到寄存器JA的输入端,这里选用右移方式,则把和Si接到右移输入端DSR,JB寄存器数据仍送回JB中。

接线完毕,先预清:JA=0,JB=0,进位触发器D为零;然后置数:JA=1010,JB=0101(置数方法参考74LS194基本功能验证方法)。输入移位脉冲,进行JA+JB➝JA的运算。输入4个脉冲,一次运算完成,此时JA应该为1111,JB应该为0101,若结果不是此数,则出错,应找到出错原因;若运算结果正确,再更换JA和JB另一组数据,进行JA+JB➝JA的操作。

4)预习要求

(1)复习数据寄存器、移位寄存器的工作原理和逻辑电路。

(2)预习中规模集成电路74LS194双向移位寄存器的逻辑功能、管脚排列及其各种应用方法。

5)实验报告

(1)画出各实验电路和时序状态图。

(2)设计由74LS194构成8位、16位移位寄存器的方法,并实现M=25的自启动扭环形计数器。

6)实验设备

(1)数字电路实验系统(SDS-Ⅵ)一台

(2)集成电路:74LS74、74LS112、74LS08、74LS194、74LS04、74LS00、74LS183各一片

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。