1)实验目的

(1)学习用触发器构成各种计数器的方法。

(2)测试各种计数器的逻辑功能和波形图,了解同步计数器与异步计数器的区别。

(3)掌握利用集成计数器构成任意进制计数器的原理和方法。

2)实验原理

计数器是典型的时序逻辑电路,它用来累计和记忆输入脉冲的个数。计数是数字系统中很重要的基本操作,集成计数器是应用最广泛的逻辑部件之一。

计数器种类较多,分类方法也有多种。按构成计数器中的多个触发器是否使用同一个时钟脉冲源来分,有同步计数器和异步计数器;根据计数进制的不同,分为二进制计数器、十进制计数器和任意进制计数器;根据计数的增减趋势,又分为加法、减法和可逆计数器;还有可预置计数和可编程序功能计数器等。

(1)用D触发器构成异步二进制加/减法计数器

由于双稳态触发器有“1”和“0”两个状态,所以一个触发器可以表示一位二进制数。如果要表示n位二进制数,就得用n个触发器。

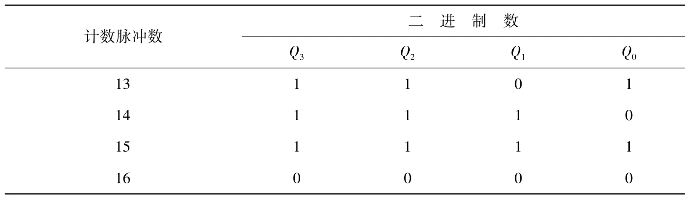

我们可以列出4位二进制加法计数器的状态表(表4.24)。

表4.24 二进制加法计数器的状态表

续表4.24

要实现表4.24所列的4位二进制加法计数,必须用4个双稳态触发器,它们具有计数功能。采用不同的触发器可以有不同的逻辑电路。即使用同一种触发器也可以得出不同的逻辑电路。

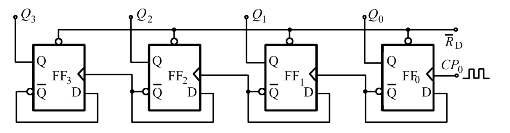

图4.54 4位二进制异步加法计数器

如图4.54所示是用4只D触发器构成的4位二进制异步加法计数器,其连接特点是将D触发器接成T′触发器,再由低位触发器的![]() 端和高一位的CP端相连。

端和高一位的CP端相连。

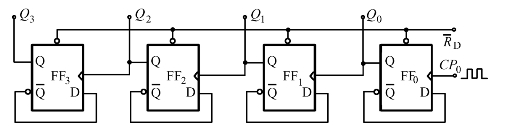

如果将图4.54稍加改动,即将低位触发器的Q端与高一位的CP端相连,即可构成一个4位二进制减法计数器,如图4.55所示。

图4.55 4位二进制异步减法计数器

(2)集成计数器的应用

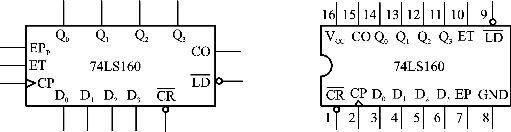

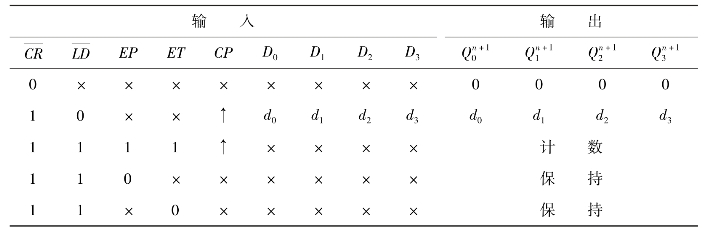

①74LS160为十进制可预置同步计数器,其逻辑符号和管脚图如图4.56所示,功能表如表4.25所示。

图4.56 74LS160逻辑符号及管脚图

74LS160计数器有下列输入端:异步清零端![]() (低电平有效),时钟脉冲输入端CP,同步并行预置数控制端

(低电平有效),时钟脉冲输入端CP,同步并行预置数控制端![]() (低电平有效),计数控制端ET和EP,并行数据输入端D0~D3。

(低电平有效),计数控制端ET和EP,并行数据输入端D0~D3。

74LS160计数器有下列输出端:4个触发器的输出Q0~Q3,进位输出CO,进位输出端CO通常为0,仅当计数控制端ET=1且计数器状态为9时它才为1。

表4.25 74LS160的功能表

根据功能表4.25,可看出74LS160具有以下功能:

a.异步清零功能。若![]() ,不论其他输入端(包括CP端)为何种状态,均实现4个触发器全部清零。由于这一清零操作不需要时钟脉冲CP配合(即不论CP是什么状态都行),所以称为“异步清零”。

,不论其他输入端(包括CP端)为何种状态,均实现4个触发器全部清零。由于这一清零操作不需要时钟脉冲CP配合(即不论CP是什么状态都行),所以称为“异步清零”。

b.同步并行置数功能。当![]() 且

且![]() 时,在CP上升沿的作用下,触发器Q0~Q3分别接收并行数据输入信号D0~D3。由于此置数操作与CP上升沿同步,且4个触发器同时置数,所以称为“同步并行置数”。

时,在CP上升沿的作用下,触发器Q0~Q3分别接收并行数据输入信号D0~D3。由于此置数操作与CP上升沿同步,且4个触发器同时置数,所以称为“同步并行置数”。

c.同步十进制加计数功能。当![]() 时,若计数控制端ET·EP=1,则对计数脉冲CP实现同步十进制加计数。“同步”表明各触发器动作都与CP(上升沿)同步。

时,若计数控制端ET·EP=1,则对计数脉冲CP实现同步十进制加计数。“同步”表明各触发器动作都与CP(上升沿)同步。

d.保持功能。当![]() 时,若ET·EP=0,即两个计数控制端中至少有一个为0,则不管CP状态如何,计数器中各触发器保持原状态不变。(https://www.daowen.com)

时,若ET·EP=0,即两个计数控制端中至少有一个为0,则不管CP状态如何,计数器中各触发器保持原状态不变。(https://www.daowen.com)

综上所述,74LS160是具有异步清零功能的可置数十进制同步计数器。

②利用输出信号对输入端的不同反馈(有时需加少量门电路),74LS160可以实现任意进制的计数器。

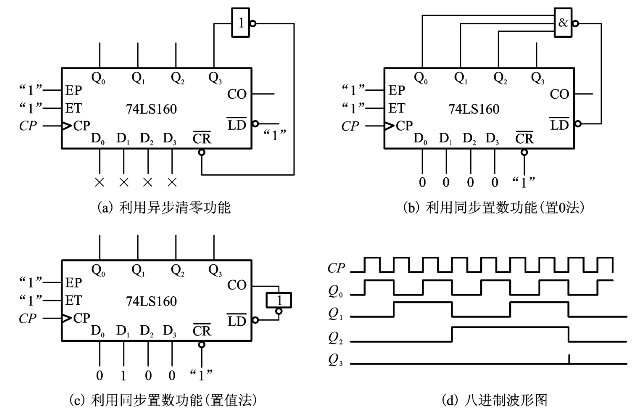

例:用74LS160实现八进制计数器。

a.M=8,用一片74LS160即可。图4.57(a)为利用异步清零功能构成的八进制计数器。设初态全为0,则在前7个计数脉冲作用下,Q3Q2Q1Q0均按十进制规律正常计数,而当第8个计数脉冲上升沿到来后,Q3Q2Q1Q0的状态变为1000,通过反相器使![]() 从平时的1变为0,借助异步清零功能,使4个触发器全部清0,从而中止了“十进制”的计数趋势,实现了自然态序模8加计数。注意:主循环中的8个状态是0000至0111,它们各延续一个计数脉冲周期;而1000只是一个瞬态,实际上它只停留短暂的一瞬,如图4.57(d)中的波形图所示。

从平时的1变为0,借助异步清零功能,使4个触发器全部清0,从而中止了“十进制”的计数趋势,实现了自然态序模8加计数。注意:主循环中的8个状态是0000至0111,它们各延续一个计数脉冲周期;而1000只是一个瞬态,实际上它只停留短暂的一瞬,如图4.57(d)中的波形图所示。

b.图4.57(b)为利用同步置数功能构成的八进制计数器,在Q3Q2Q1Q0为0111的状态下,准备好置数条件——![]() ,这样,在下一个计数脉冲上升沿到来后,就不再实现“加1”计数,而是实现同步置数,Q3Q2Q1Q0接收“并行数据输入信号”,变成0000,从而满足了模8的要求。此方法可称为借助同步置数功能的置全零法。

,这样,在下一个计数脉冲上升沿到来后,就不再实现“加1”计数,而是实现同步置数,Q3Q2Q1Q0接收“并行数据输入信号”,变成0000,从而满足了模8的要求。此方法可称为借助同步置数功能的置全零法。

图4.57 用74LS160构成八进制计数器

c.图4.57(c)为利用同步置数功能构成八进制计数器的另一种方法。要求的模M=8,因而多余的状态数=10-8=2,十进制数2对应BCD码是0010,于是如果在1001状态下准备好同步置数条件,且“并行数据输入”D3D2D1D0分别接0010,则下一个计数脉冲上升沿就能使Q3Q2Q1Q0不变成0000,而转为0010,这样就跳过了0000至0001两个状态,实现了模8计数。该方法充分利用了1001状态下CO才为1的特点。我们把这种方法称为借助同步置数功能的置值法。

3)实验内容

(1)D触发器我们还是选用74LS74双上升沿D触发器,用两片74LS74构成异步二进制加/减法计数器。

①先按图4.54接线,验证异步二进制加法器的功能,![]() 接逻辑开关,将CP0时钟端接单次脉冲源,输出端Q3、Q2、Q1、Q0接LED,

接逻辑开关,将CP0时钟端接单次脉冲源,输出端Q3、Q2、Q1、Q0接LED,![]() 接高电平+5 V。

接高电平+5 V。

②清零后,逐个送入单次脉冲,观察并记录Q3、Q2、Q1、Q0的状态。

③将单次脉冲改为1 Hz的连续脉冲,观察Q3、Q2、Q1、Q0的状态。

④将CP0再改为1 kHz的连续脉冲,用示波器观察Q3、Q2、Q1、Q0端的波形。

⑤再按图4.55接线,验证异步二进制减法器的功能。重复上述步骤,并列表记录输出波形(表格自拟)。

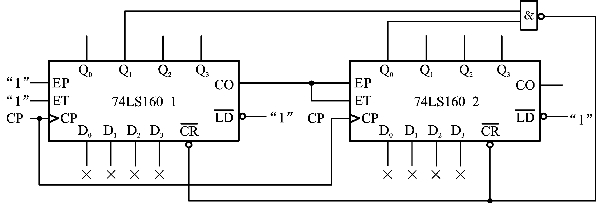

(2)用74LS160实现十二进制计数器。

①利用异步清零功能构成十二进制计数器的电路如图4.58所示。因为M=12,所以用两片74LS160,两片74LS160的CP端直接与计数脉冲相连,构成一个同步计数器,并将低位片(1)的进位输出CO送到高位片(2)的计数控制端ET和EP。由于构成的计数器的模为12,因此清零条件为![]() (注:

(注:![]() 为第1片74LS160的输出Q1,

为第1片74LS160的输出Q1,![]() 为第2片74LS160的输出Q0),即当两片计数器计数到12时,产生一个清零信号,使计数器整体置零。

为第2片74LS160的输出Q0),即当两片计数器计数到12时,产生一个清零信号,使计数器整体置零。

②按图4.58接线,验证十二进制计数器的功能,将CP时钟端接单次脉冲,输出端接LED。

③逐次送入单次脉冲,观察并记录两片74LS160的输出脉冲状态。

④将单次脉冲改为1 Hz的连续脉冲,观察两片74LS160的输出状态。

⑤将CP时钟端接1 kHz的连续脉冲,用示波器观察两片74LS160的输出端的波形。

图4.58 74LS160构成的十二进制计数器(异步清零)

4)实验报告

(1)画出各实验电路对应的逻辑图、状态表、波形图。

(2)总结二进制、十二进制波形图的特点,分析其原因。

5)实验设备

(1)数字电路实验系统(SDS-Ⅵ)一台

(2)双踪示波器(YB4320C)一台

(3)集成电路:74LS112、74LS74、74LS160、74LS00各两片

6)思考题

(1)设计由4只JK触发器构成的异步十进制加法计数器电路。

(2)画出利用74LS160的同步置数功能实现十二进制计数器的电路图。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。