1)实验目的

(1)掌握几种所学触发器的逻辑功能及其测试方法。

(2)了解触发器触发方式的测试方法。

(3)了解用触发器设计简单实用电路的基本方法。

2)实验原理

触发器是一个具有记忆功能的二进制信息存储器件,是构成各种时序电路的最基本逻辑单元。触发器具有两个稳定状态,用逻辑状态“0”和“1”来表示。在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。

图4.49 基本RS触发器

(1)基本RS触发器

图4.49为由两个与非门交叉连接构成的基本RS触发器。基本RS触发器具有置“0”、置“1”和“保持”三种功能。通常称![]() 为置“1”端,因为

为置“1”端,因为![]() 时触发器被置“1”;

时触发器被置“1”;![]() 为置“0”端,因为

为置“0”端,因为![]() 时触发器被置“0”;当

时触发器被置“0”;当![]() 时状态保持。基本RS触发器也可以用两个“或非门”组成,此时为高电平触发器。

时状态保持。基本RS触发器也可以用两个“或非门”组成,此时为高电平触发器。

(2)JK触发器

在输入信号为双端的情况下,JK触发器是功能完善、使用灵活和通用性较强的一种触发器。本实验采用74LS112双JK触发器,是下降边沿触发的边沿触发器。管脚功能及逻辑符号如图4.50所示。JK触发器常被用作缓冲存储器、移位寄存器和计数器。JK触发器的状态方程为:

![]()

J和K是数据输入端,是触发器状态更新的依据。Q与![]() 为两个互补输出端。通常把Q=0、

为两个互补输出端。通常把Q=0、![]() 的状态定为触发器“0”状态,而把

的状态定为触发器“0”状态,而把![]() 定为“1”状态。

定为“1”状态。

图4.50 74LS112双JK触发器管脚功能及逻辑符号

下降边沿触发JK触发器的功能表如表4.19所示。

表4.19 JK触发器的逻辑功能

(3)D触发器

在输入信号为单端的情况下,D触发器用起来最为方便,其状态方程为:Qn+1=D。其状态的更新发生在CP脉冲的上升沿,故又称之为上升沿触发的边沿触发器。触发器的状态只取决于时钟脉冲到来时刻D端的状态。

D触发器应用很广,可用做数字信号的寄存、移位寄存、分频和波形发生器等。

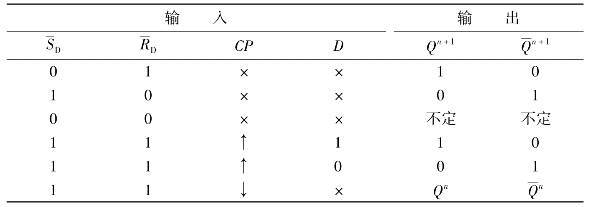

实验选用的是74LS74双上升沿D触发器,其管脚排列及逻辑符号如图4.51所示。其功能表如表4.20所示。

图4.51 74LS74管脚排列及逻辑符号

表4.20 D触发器的逻辑功能

3)实验内容

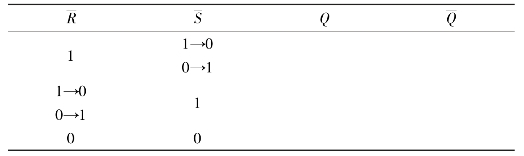

(1)测试基本RS触发器的逻辑功能

按图4.49接线,用两个与非门组成基本RS触发器,输入端![]() 接逻辑开关,输出端Q、

接逻辑开关,输出端Q、![]() 接LED,按表4.21要求测试,并记录结果。

接LED,按表4.21要求测试,并记录结果。

表4.21 基本RS触发器的逻辑功能

(https://www.daowen.com)

(https://www.daowen.com)

(2)测试JK触发器74LS112逻辑功能

①按表4.22的要求改变J、K、CP的状态,观察![]() 状态变化,观察Q端的状态更新是否发生在CP脉冲的下降沿(即CP由1→0),并记录之。

状态变化,观察Q端的状态更新是否发生在CP脉冲的下降沿(即CP由1→0),并记录之。

②J=K=1,CP端输入1 kHz连续脉冲,用双踪示波器观察并描绘CP、Q端波形图(注意触发方式和分频情况)。

表4.22 JK触发器的逻辑功能测试表

(3)测试D触发器74LS74的逻辑功能

①按表4.23进行测试,并观察触发器状态更新是否发生在CP脉冲的上升沿(即0→1),记录在表4.23中。

②![]() ,CP端输入1 kHz的连续脉冲,用双踪示波器观察并描绘CP、Q端波形图(注意触发方式和分频情况)。

,CP端输入1 kHz的连续脉冲,用双踪示波器观察并描绘CP、Q端波形图(注意触发方式和分频情况)。

表4.23 D触发器的逻辑功能测试表

(4)用D触发器设计一个三人抢答器,设计任务和要求:

①设计一个可供三名选手参赛的抢答器,他们的编号分别是A、B、C,每名选手控制一个抢答开关,分别是K1、K2、K3,以控制自己的一个LED指示灯。

②为主持人设置一个控制开关,用来控制抢答器的清零和抢答的开始。

③抢答器具有锁存和显示的功能。抢答开始后,第一抢答者拨动抢答开关后,通过LED显示第一抢答者,同时封锁输入电路,其他人再抢无效。第一抢答者的LED一直保持到主持人将系统清零为止。

由D触发器构成的三人抢答器电路如图4.52所示。

电路工作原理:抢答前主持人将复位开关先置于“0”对系统清零,使QA、QB、QC均为“0”,同时A、B、C三人的抢答开关K1~K3初始状态均为“0”。抢答时主持人将复位开关置于“1”,若A先将对应的开关K1拨至“1”,则A对应触发器的DA为“1”,在与非门输出的1 024 Hz的脉冲CPA作用下,QA由初始的“0”翻转为“1”,A对应的LED指示灯点亮,同时![]() 为“0”,使与非门的输出为“1”,即三个D触发器的CP脉冲输入全为“1”,此时无上升沿脉冲信号,从而封锁了B和C对应的触发器,抢答成功。抢答完后由主持人拨动复位开关使第一抢答者的指示灯熄灭,并解除封锁,以便进行下一轮抢答。

为“0”,使与非门的输出为“1”,即三个D触发器的CP脉冲输入全为“1”,此时无上升沿脉冲信号,从而封锁了B和C对应的触发器,抢答成功。抢答完后由主持人拨动复位开关使第一抢答者的指示灯熄灭,并解除封锁,以便进行下一轮抢答。

图4.52 三人抢答器电路图

4)实验报告

(1)整理实验数据、图、表,对实验结果进行分析。

(2)根据实验结果总结触发器的逻辑功能和触发方式。

5)实验设备

(1)数字电路实验系统(SDS-Ⅵ) 一台

(2)双踪示波器(YB4320C)一台

(3)集成电路:74LS00、74LS112、74LS74各一片

6)思考题

(1)D触发器在时钟脉冲作用下,触发器状态等于什么?当触发器状态等于D输入端信号后,若D不变,再来时钟脉冲,触发器状态会不会再翻转?如果要使D触发器处于计数状态,则输入端应处于什么状态?画出逻辑图。

(2)时钟触发器的触发方式有几种?它们的主要特点是什么?

(3)一个T触发器的时钟输入端输入频率为f的脉冲源,试问触发器输出脉冲的频率为多少?若再经过一个触发器后,频率为多少?为什么?

(4)如图4.53(a)是一个机械式的接触开关,由于机械的弹性作用,都会在扳动时来回跳几次,而图4.53(b)是一个去抖动开关,试分析该电路为什么没有反跳现象?

图4.53 机械式接触开关和去抖动开关

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。