1)实验目的

(1)熟悉TTL与非门的外形和管脚引线排列。

(2)通过测试了解与非门的直流参数。

2)实验原理

(1)数字集成电路的两大系列

①TTL——Transistor-Transistor Logic晶体管-晶体管逻辑电路

74LS系列集成电路(低功耗肖特基TTL电路)是一种比较理想且使用最广的器件。

②CMOS——Complementary-Symmetry Metal-Oxide-Semiconductor Circuit互补对称式金属-氧化物-半导体电路

(2)TTL与非门直流参数的测量

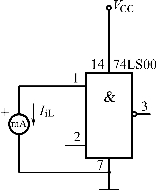

图4.1 ICCL测试电路

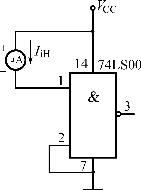

图4.2 IiL测试电路

图4.3 IiH测试电路

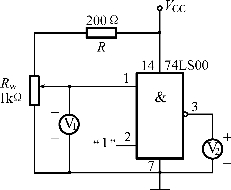

图4.4 电压传输特性测试电路

图4.1是低电平输出电源电流ICCL(当输入端全为高电平时,流入电源端的电流)测试电路;图4.2是低电平输入电流IiL(当某一输入端接低电平,其余输入端接高电平时,从该输入端流出的电流)测试电路;图4.3是高电平输入电流IiH(当某一输入端接高电平,其余输入端接低电平时,流入该输入端的电流)测试电路;图4.4是测量电压传输特性(输出电压Uo与输入电压Ui之间的关系,将某一输入端的电压从零逐渐增大,而将其他输入端接高电平)的电路;图4.5是测量扇出系数No(指与非门电路可带同类门的个数,将任一输入端接开门电平UON=1.8 V,其余输入端悬空,调节电位器使Uo=0.35 V,负载电流为IoL,No=IoL/IIL)的电路。

图4.5 扇出系数测试电路

图4.6 平均传输延迟时间tpd

图4.7 环形振荡器电路

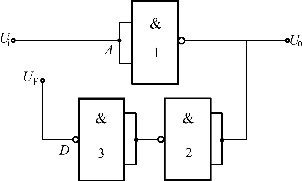

(3)测平均传输延迟时间

在与非门输入端加上一个脉冲电压,则输出电压将有一定的时间延迟,表明延迟时间的输入、输出电压波形如图4.6所示。从输入脉冲上升沿的50%处起到输出脉冲下降沿的50%处的时间称为上升延迟时间tpd1;从输入脉冲下降沿的50%处起到输出脉冲上升沿的50%处的时间称为下降延迟时间tpd2。tpd1与tpd2的平均值称为平均传输延迟时间tpd,此值越小越好。

由图4.7所示的环形振荡器测出平均传输延迟时间tpd,如果每个与非门的tpd都相等,则振荡信号的周期T=6tpd,于是

tpd=T/6

为了证明上述自激振荡过程,将图4.7中的反馈线AD断开,如图4.8所示,然后在门1的输入端加入一个频率合适的方波Ui,同时观察Ui、Uo和UF波形(以Ui作同步信号),如图4.9所示,Uo是Ui反相后右移tpd的波形,如果Ui的频率符合振荡所需的相移条件,即Ui比Uo恰好右移2tpd,则3tpd=tp。

图4.8 断开反馈线的环形振荡器

图4.9 Ui、Uo和UF波形(https://www.daowen.com)

式中,tp为Ui的脉冲宽度。则图4.7将输出周期为T的方波,显然

T=2×3tpd=6tpd

所以tpd=T/6

电路依靠合闸时的扰动电压起振。

图4.10 电压传输特性曲线

3)实验内容

(1)根据与非门的逻辑功能检查与非门是否良好。

(2)测量下列各直流参数:

①低电平输出电源电流ICCL(图4.1)。

②低电平输入电流IiL(图4.2)。

③高电平输入电流IiH(图4.3)。

④电压传输特性(图4.4),完成表4.1,并画出电压传输特性曲线(完成图4.10)。

⑤扇出系数No(图4.5)。

⑥平均传输延迟时间tpd(图4.7)。

表4.1 电压传输特性测量表

4)预习要求

阅读所用与非门(74LS00)的说明书,了解其线路、引线排列、逻辑功能和参数。

图4.11 74LS00管脚排列图

5)实验报告

列出直流参数的实测数据表格。画出传输特性曲线,确定UOFF、UON、UoL、UoH值,与手册参数相比,判断所测的电参数是否合格。

6)实验设备

(1)双踪示波器(YB4320C) 一台

(2)指针式万用表(MF-47)一台

(3)直流稳压电源(YB1732C2A)一台

(4)数字电路实验系统(SDS-Ⅵ)一台

(5)参考元件:74LS00(二输入端四与非门)管脚排列如图4.11所示。

7)思考题

(1)与非门在什么情况下输出高电平?在什么情况下输出低电平?其不用的输入端如何处理?

(2)CMOS器件和TTL器件各有什么特点?在什么场合适合选用CMOS器件?

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。