1.实现过程

用Hopfield神经网络来表达人脑的联想记忆这一功能。并采用EWB或Multisim软件来形成原理图,即用这些软件提供的仿真元器件进行连接,用元器件组成神经元,再把这些神经元连接成Hopfield反馈网络,但这个方案遇到了困难。首先是设定网络的初始状态有困难,设定后无法撤销初始状态使其自动运行。其次是数目过多的神经元使加权相加的实际实现发生困难,要用一个相加器实现15个数字的相加是非常不容易的。再次,电原理图所模仿的神经元网络需要有能量的提供,可是理论上的网络找不到能量输入的环节,因此网络的自动运行便无法实现。图2-29是用EWB所做的电原理图,为简便起见,这里用了三个神经元来说明原理:

图2-29 用EWB所做的三个神经元的电原理图

鉴于以上原因,改用VHDL来编写程序,实现神经元网络的连接与模拟。这样可以做到不关心网络内部的具体结构,从而解决了找不到神经元电路的具体实现以及无法正确地将这些电路连接到一起而实现联想记忆网络的问题。在计算机上用VHDL编写成功后,还可以直接进行编译、综合、模拟记忆以及仿真,最后如果成功仿真,还可下载到FPGA板上,进行硬件实现,所以更为直观。

在编写的过程中,开始时的设计是要设计in_1_1,in_1_2等16个输入端口和1_1_1,1_1_2等16个与之对应的输出端口,实际上就是设想中的16个小灯组成的4×4的矩阵。W_1_1、W_1_2分别代表神经元1到神经元1、2的连接权值,直到W_16_16,共256个连接权值。设m1,m2,…,m16,共16个中间变量,h_1~h_16共16个比较变量,用于比较加权后的结果与0之间的大小关系。由于输入与输出都是位运算,即0或者1两种状态,因此在计算过程中要变为-1和1两种状态,这样既简便易懂又与理论贴近,这就需要把输入赋值给中间变量的过程中转换状态,最后再把计算结果变成0和1输出。在由输入给中间变量赋值的过程中,开始采用LOOP(循环)语句赋值,即

但是在VHDL中,不像C++语言中的变量赋值那样可以直接对an(i)这样的变量进行循环赋值。而在VHDL语言中,变量加编号只能用下划线“_”连接,写成an_i,因此不能用上面那个循环语句进行直接循环赋值。因此要将输入输出的类型改为总线型结构,即可循环赋值,即an:INOUT BIT_VECTOR(16 DOWNTO 1);an为16位总线结构,输入输出双向端口。但由于中间变量m仍然是一个一个的单独变量,所以放弃用循环赋值,而改用IF…ELSE语句进行赋值,即

IF(an(1)=′0′)THEN

m1:=-1;

ELSE

m1:=1;

END IF;

这个语句用16次,即可将输入转化为中间变量要使用的-1和1两值状态。

h是每个神经元的加权和,用以和0比较大小进而决定该神经元下一个时刻的输出。加权语句为

h_1:=m2∗w_2_1+m3∗w_3_1+m4∗w_4_1+m5∗w_5_1+m6∗w_6_1+m7∗w_7_1+m8∗w_8_1+m9∗w_9_1+m10∗w_10_1+m11∗w_11_1+m12∗w_12_1+m13∗w_13_1+m14∗w_14_1+m15∗w_15_1+m16∗w_16_1;

其中,各个m为其他神经元本时刻的输出;w为对应的权值,在程序开始时已经根据目标状态由计算得出并设定好。共有16个这样的语句,分别与16个神经元的判断机制相对应。

得出相加结果后,再用IF语句判断其与0的大小关系,并依此为输出及下一个状态赋值。其语句如下:

IF(h_1>0)THEN

an(1)<=′1′;

ELSE

an(1)<=′0′;

END IF;

同样,这样的语句有16个,将计算结果又返回给神经元的输出而显示出来,同时又为下一次计算准备了数据。

上述整个过程都是嵌套在一个大的循环里面,这个循环用IF语句引导,以时钟信号的上升沿为激活信号,使得每有一个时钟上升沿来临时,系统运行一次计算,这样一直迭代计算下去。其语句为

IF(clk′EVENT AND clk=′1′)THEN

END IF;(https://www.daowen.com)

接下来进入调试阶段。

在调试时,首先权值的设定出现问题。权值是根据所设定的状态按公式推算出来的。记住的状态是图形“4”,根据计算,除了对自身的反馈权值为0外,其他的反馈权值都为0.0625或-0.0625。在编译时,系统报错,经查阅资料发现MAX+plusⅡ开发软件不支持浮点型数据的计算,这就说明这样的权值是不可以的。由于h是m与权值相乘后相加的结果,而后还要与0做比较,所以想到可以在两边都同时乘以相应的倍数,结果不变。这样,0乘以任何数还是0,而h式里面的15个权值就可以乘以10000,而变成625或-625这样的整数加以运算了。这样改过之后,消除了语法上的错误,开始进行编译和综合过程。

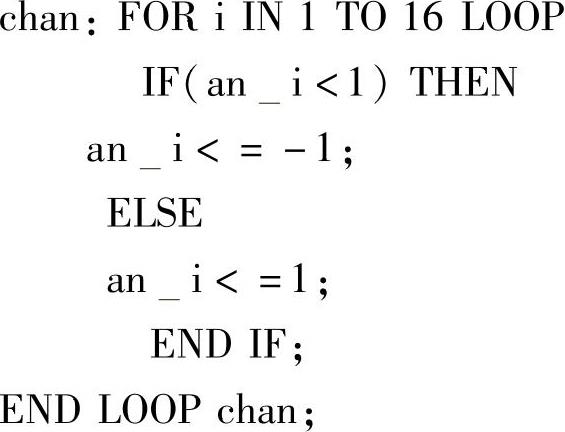

图2-30 部分程序界面

2.实验结果

下面是整个过程的说明以及相关的图片和演示。图2-30是部分程序界面。

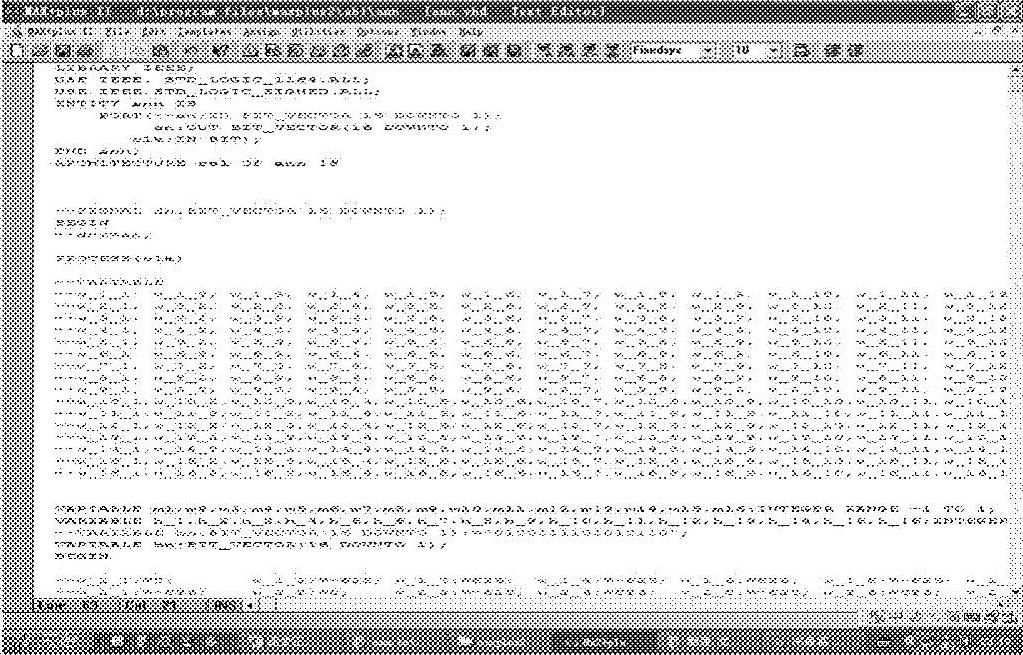

程序调通后开始编译过程,图2-31就是编译通过后的情景。

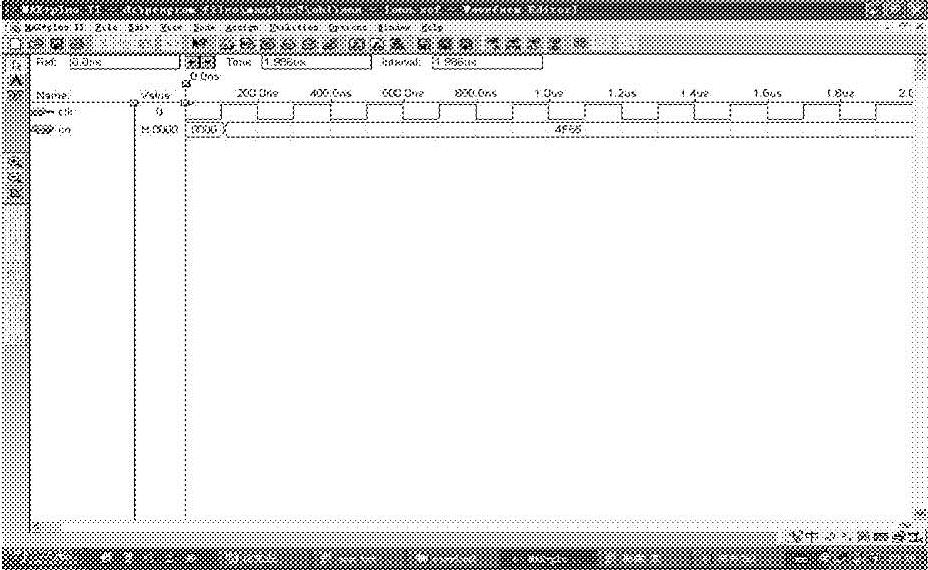

仿真通过后可以打开波形图察看仿真结果,图2-32是仿真结果波形。

从图2-32中可以看到输入信号为时钟信号clk,输出为cn,它们在图中的模式都是16位总线结构,用4位十六进制数来表示。输出的初始值为0,当第一个上升沿来临时,系统开始计算,从而使系统的输出状态达到稳定状态4F55。

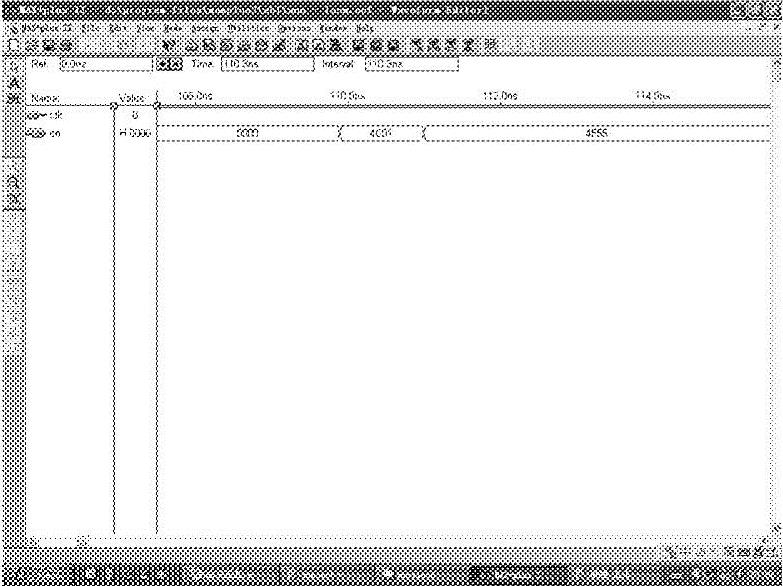

其实,系统是经过计算而逐步趋向于稳定态4F55的,只是由于设定的目标模式较少,比较简单,而加快了趋向过程,从而看不到中间的去向步骤。但是将波形图放大,还是会看见一些中间的不稳定状态,从而证明了系统的逐步趋向性,图2-33就是放大波形图后看到的中间环节。

最后,这个系统还在FPGA现场可编程门阵列器件上得以硬件实现。图2-34就是在硬件上显示结果的照片。

图2-31 编译通过后界面

可以看见,逻辑器件板上的右上方有一排16个小灯,从左至右分别代表输出cn1~cn16。

照片上显示的就是输出达到稳定的目标状态的时刻。如果小灯亮为1、灭为0,则可以看见小灯的亮灭情况为“1010 1010 1111 0010”。虽然这款板子上没有4×4的矩阵形小灯,但通过重置,仍可以直观地看到结果。

图2-32 仿真结果波形

图2-33 放大波形图后看到的中间环节

图2-34 在硬件上显示的实验结果

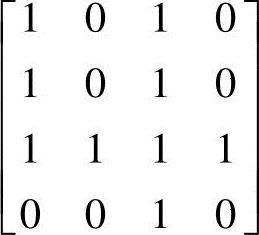

如果把这些小灯从左至右每4个为一个横行,就可以排成一个4×4的矩阵,显示如下:

我们可以清晰地看到,预先设定的目标模式图形“4”,显示在我们面前。

本节采用EDA构建了Hopfield神经网络电路,用于模拟联想记忆功能的部分人脑功能,让电路识别与曾经记忆过的模式大体相仿但又不尽相同的模式时,能够联想起记忆过的模式,并逐步趋向于输出初始记忆模式。但是这个研究还不深入,实现的功能还很简单,它只是给出了一种人工大脑的实现思路,未来的电子技术和神经科学以及人工智能技术相结合研究的道路还很长。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。