AC/DC LED驱动电源交流输入电压如式(9-10)。若PF=1,且输出功率恒定,

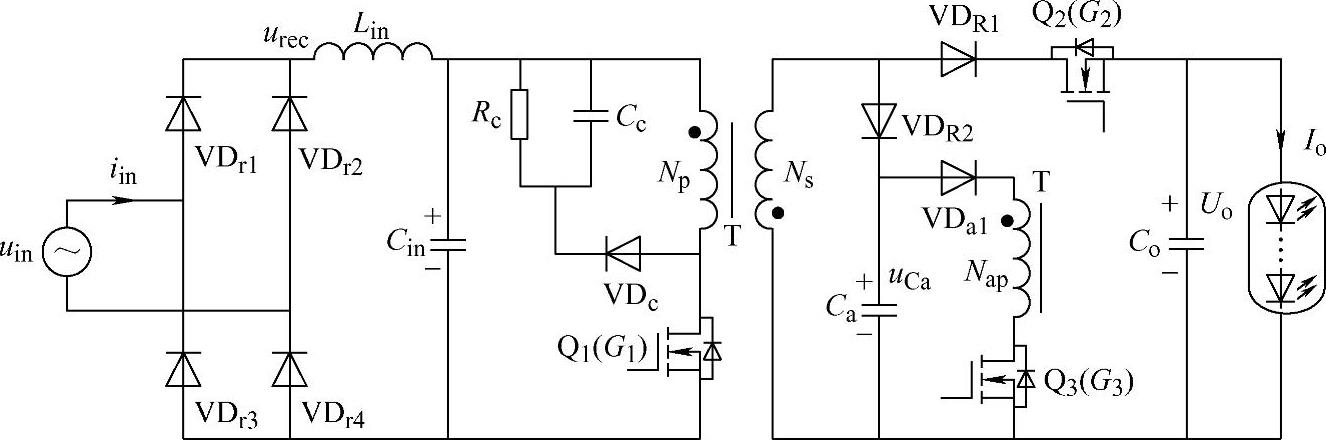

图9-27 IDFC主电路拓扑

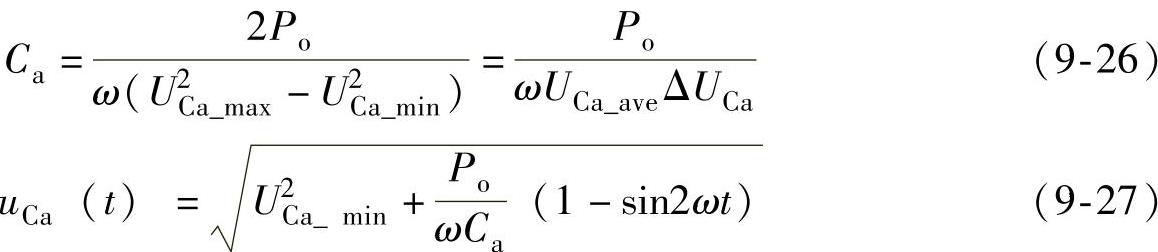

那么储能电容的电容值和电压表达式为[7]

式中,UCa_max、UCa_min分别为uCa的峰值和谷值;UCa_ave为uCa的电压平均值;ΔUCa=UCa_max-UCa_min。

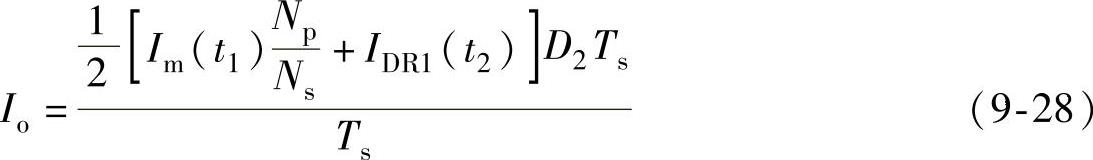

为了保证输出电流恒定,在不同功率条件下,一个开关周期内流过负载的平均电流Io都必须相等,因此:

当pin>po时,根据式(9-15)、式(9-16)和图9-23有

当pin<po时,根据式(9-22)、式(9-24)和图9-25有

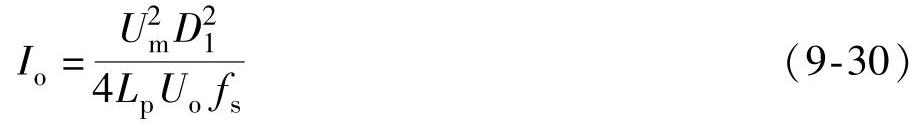

对于工作在DCM的具有PFC功能的Flyback变换器有

式中,fs为开关频率,fs=1/Ts。

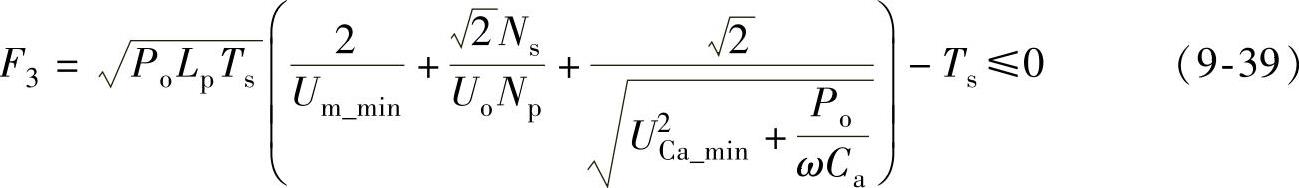

为实现PFC功能,Flyback变换器工作在电流断续模式,故当pin>po时和pin<po时分别应满足一定的边界条件如下。

(1)当pin>po时,需要满足公式(9-20)的条件。

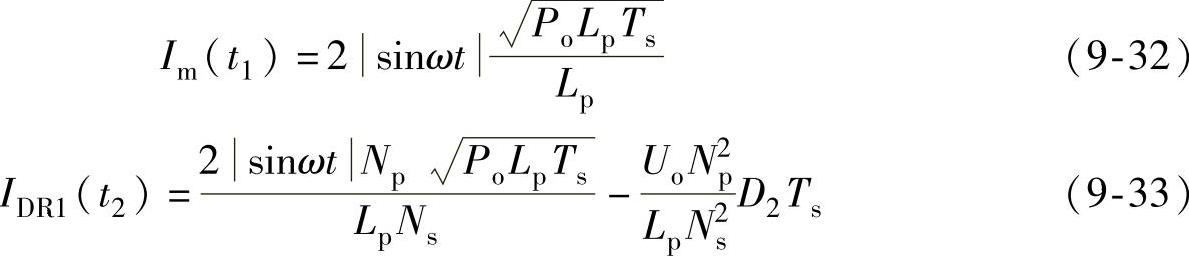

根据式(9-30)有

将式(9-31)代入式(9-15)、式(9-16)得

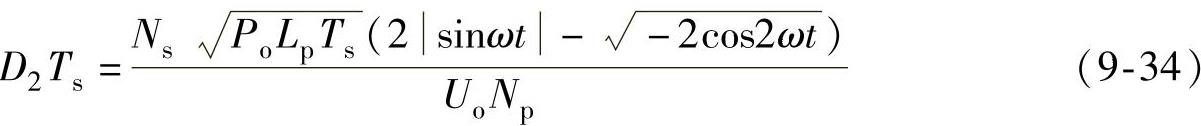

将式(9-30)、式(9-31)、式(9-32)、式(9-33)代入式(9-28)解方程可得

对式(9-34)求导得

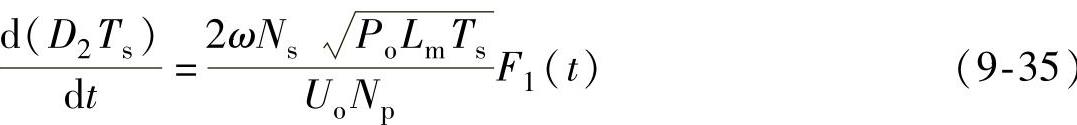

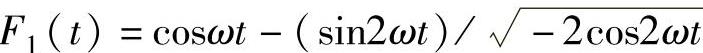

式中, 。

。

其中p/4≤ωt≤3p/4,故F1(t)<0,故D2Ts为单调减函数。

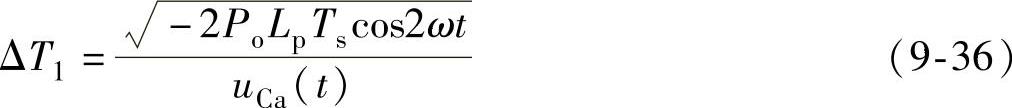

将式(9-31)、式(9-34)代入式(9-19)得(https://www.daowen.com)

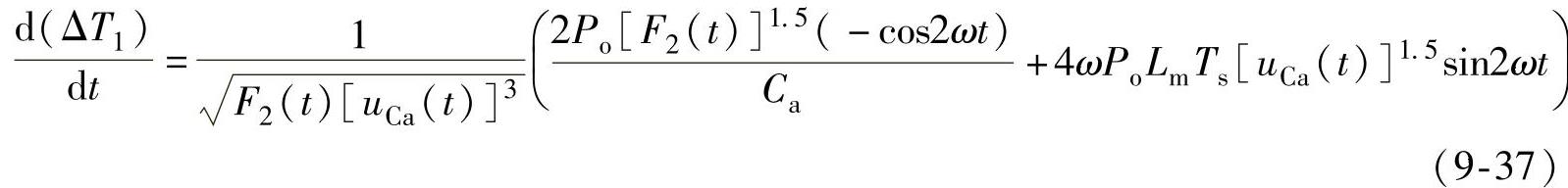

对式(9-36)求导得

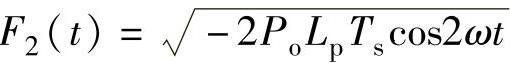

式中, 。

。

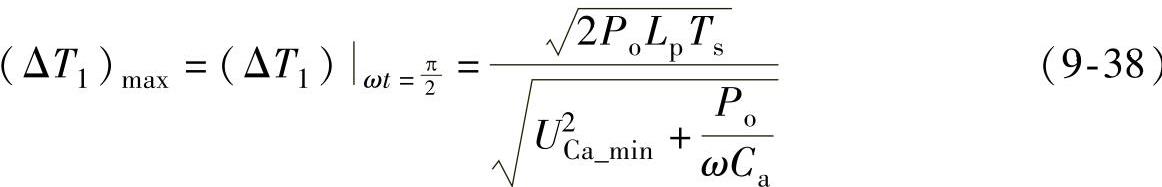

当p/4≤ωt≤p/2(pin>po),-cos2ωt和sin2ωt均大于零,所以式(9-37)大于零,ΔT1的函数递增,最大值为

当p/2≤ωt≤3p/4(pin>po),uCa(t)和-cos2ωt均是递减的,由式(9-36),可知ΔT1在ωt=p/2处取得最大值。

由式(9-20)、式(9-31)和式(9-38)得出,当pin>po时需要满足的边界条件为

(2)当pin<po时,需要满足公式(9-25)条件。

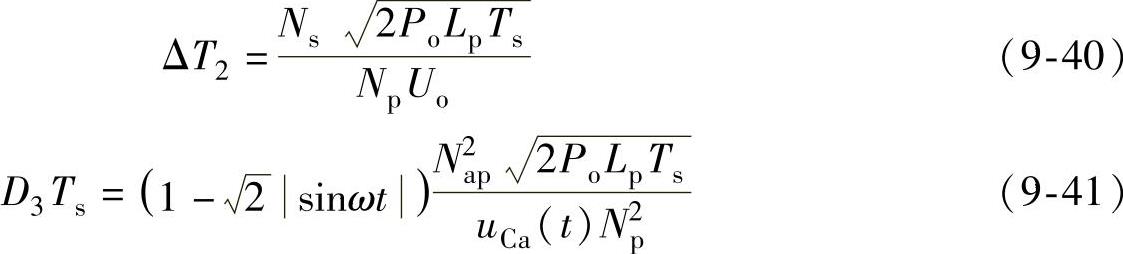

根据式(9-22)~式(9-24)和式(9-29)有

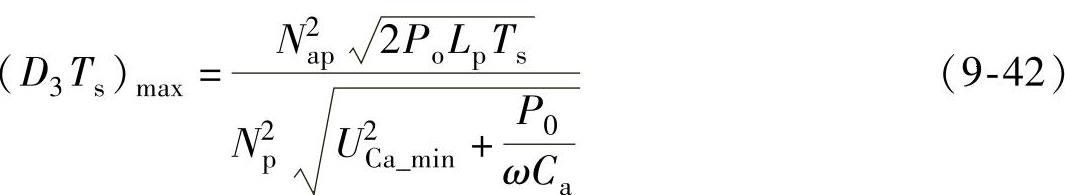

当3p/4≤ωt≤p(pin<po),uCa(t)和sinωt均是递减的,所以根据式(9-41),ΔT2在ωt=p处取得最大值,且最大值为

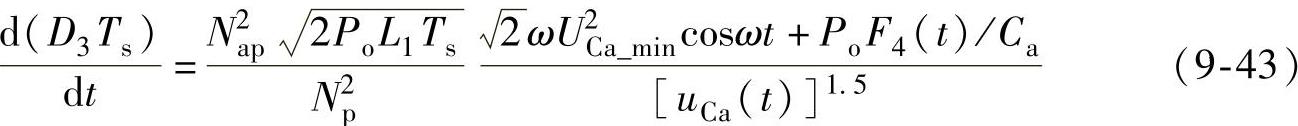

对式(9-41)在p≤ωt≤5p/4(pin<po)求导得

式中, 。

。

当p≤ωt≤5p/4(pin<po),F4(t)和cosωt都是负值,因此式(9-41)在该区间为单调递减且最大值同式(9-42)。

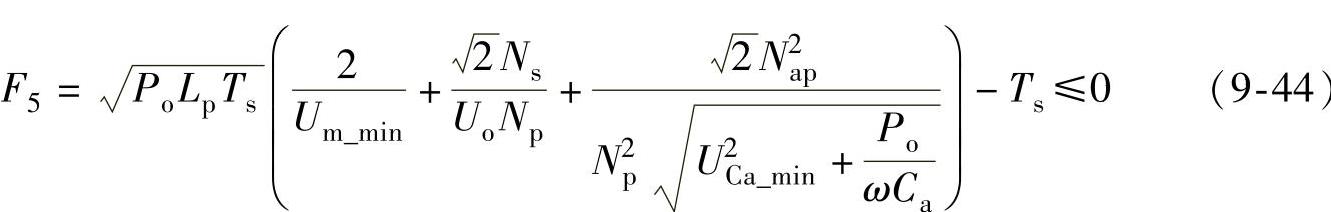

由式(9-25)、式(9-31)、式(9-40)和式(9-42)得出,当pin<po时需要满足的边界条件为

为了保证LED驱动电路稳定工作,在不同的输入功率条件下主电路参数均需满足式(9-39)、式(9-44)的边界条件。因此,可以看出需要确定的主电路参数有,Lp、Ca、UCa_min和Np∶Ns∶Nap。下面以设计实例对主电路参数设计进行说明,电路参数为,Uo=45V,Po=13.5W,Ts=10μs,Um_min=127V。

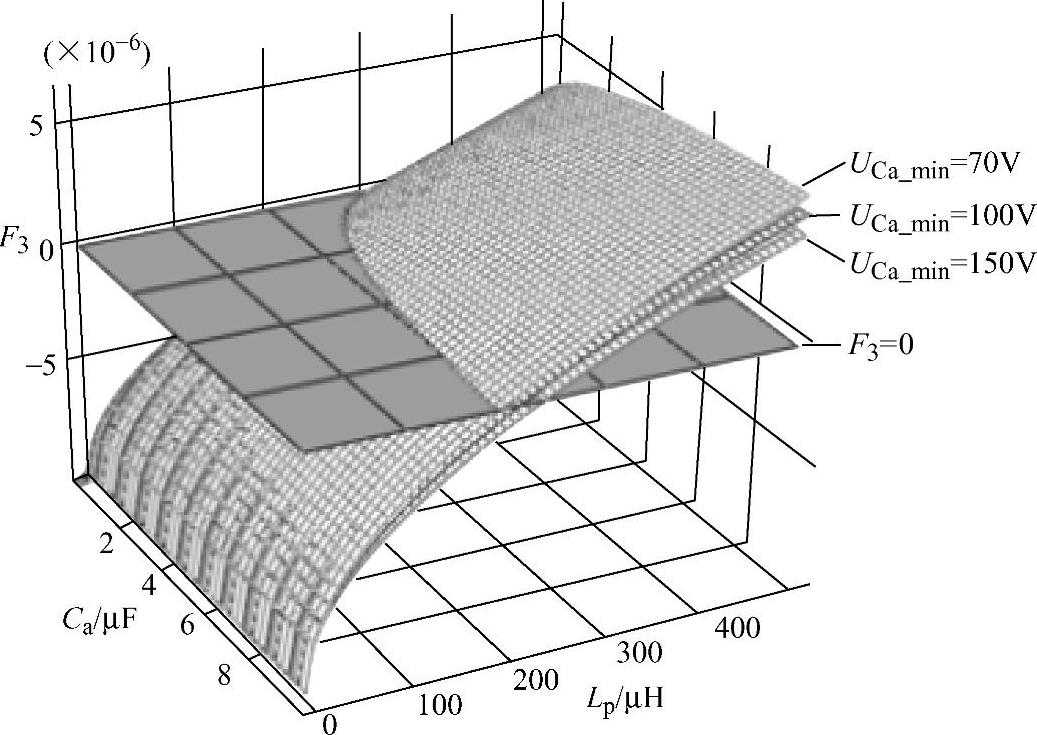

图9-28所示为式(9-39)在不同UCa_min条件下以Lp和Ca为函数变量的曲面图形,为了保证电路在pin>po时工作在DCM,Lp和Ca参数必须使F3≤0。从图中看出,当Ca和F3一定时,Lp随UCa_min变小而变小。Lp越小导致原二次侧器件所承受的电流应力越大;UCa_min越小UCa_m ax就越大,从而导致一、二次侧器件所承受的电压应力越大。同理,为了保证电路在pin<po时工作在DCM,所选的Lp也必须使式(9-44)中F5≤0。因此,在工程设计上应结合上述计算式的约束条件和实际器件选型的限制,采用验算的方法可先确定Lp和UCa_min,继而结合式(9-27)与电压纹波设计范围进行Ca和UCa_max的计算优化。

例如选择的参数为,Ca=3.3μF,Lp=85μH,UCa_min=120V,对应的时间Tpin>po和Tpin<po均小于Ts,说明所选择的参数保证了主电路在不同功率条件下都工作在DCM模式。将所确定的Ca和UCa_min代入式(9-26)可得UCa_max和UCa_ave,进而确定器件应力。

图9-28 F3在不同UCa_min条件下的曲面图形

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。