1.64×64 点阵的全彩LED 显示面板

全彩显示屏上的每个LED 灯珠包含红、绿、蓝(RGB)三种颜色的发光二极管,它们独立可控,理论上可以通过让RGB 发出不同亮度的组合产生任意想要色彩的像素。本章所要讨论的64×64点阵LED 单元板的灯珠排列如图6.2所示,它共有4 096个像素,分成64行,每行64列(像素)。该LED 面板接成共阳结构,即把每一行64个像素三色LED 的阳极都接到一起,从而形成64 条行驱动线。极限情况下,某行的每个像素都显示白色,也即每个像素的RGB 三色LED 同时点亮,该行共计有192(64×3)个LED 同时亮起。假如每个LED 平均通过5mA 的电流,要求从阳极供电线上流出近1A 的电流。所以设计面板驱动时,通常需要有行驱动管,才能提供这个行驱动必需的最大行驱动电流。

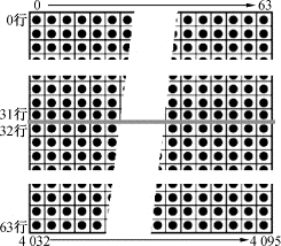

图6.2 单元板外观示意图

那么又要如何处理64个列呢?从前面章节的讨论中已经得知,像素较多的显示屏采用按行进行动态扫描的方式,即一次只显示一行,把所有行都扫描一遍,就显示了完整的一帧图像,所需要的时间称为帧扫周期。只要帧扫频率足够高,或者说帧扫周期足够短,人眼所见的就是连续平稳的一帧图像显示。之前讨论过的显示模块比较小,如8×8的模块,共有8行,一帧扫描时间内,每行将在1/8帧扫周期的时间长度上可以被点亮,这样的动态扫描方式也称为8扫,其亮度对于室内或室外的应用都足够。本章所讨论的LED 屏幕分辨率为64×64,如果也是每次只扫一行,即所谓64扫模式,每个帧扫周期内仅有1/64 的帧扫周期的时间长度上可以点亮一行,导致LED 的平均辐射能量很低,显示亮度会明显不足。为了解决这种显示亮度带来的潜在问题,实际应用中对于较大的模块,通常会将之分成若干部分同时(并行)扫描。本章所设计的显示模块将分成上、下两个半帧同时扫描,从而实现的是32扫。当然,如果希望进一步提高扫描亮度,还可以分成四块、八块并行扫描,从而得到16扫或8扫的动态扫描工作模式。这样做付出的代价是模块上承载的行驱动、行扫描、列扫描等电路元器件成倍数增加,物理成本随之成倍提高。因此,必须做出适当的取舍。我们的设计将采用32扫,可以理解成尽管物理上是一个64×64的显示屏,但它被分成上下、两个各32 行的逻辑屏,如图6.2 所示,前面0~31 行构成上半屏,后面32~63行构成下半屏,采用两组完全相同的行列扫描电路。行列扫描电路分成两组后,每组纵向列线上的64×3个LED 的阴极也都按位相连,形成64×3条列驱动线,它们将分别接到LED 恒流源驱动芯片对应的列输出驱动通道上。当行线为高电平、列线为低电平时,交叉点上的LED 将亮起,亮度取决于列驱动恒流源电流的大小。每次扫描时,需要同时准备好上、下半屏两个对应行号上的显示数据,如第0行与第32行,把它们放置到相应的列线上。由此可见,就整个屏幕而言,每一时刻同时会有两行的内容被显示,快速扫描32次,就能实现整帧图像的扫描。

2.行驱动电路

接下来讨论行驱动电路的具体实现方案。上一小节已经明确,我们将分成上、下两个半屏实现32扫,它们的驱动结构是完全相同的,只要搞清其中一个就可以了。如前所述,每行需要有一个能提供足够大驱动电流的行驱动管,能够顺序产生0~31行的共阳驱动电压与驱动电流,一次只能有一个输出有效,其余都必须保持为0,从而产生行扫信号。

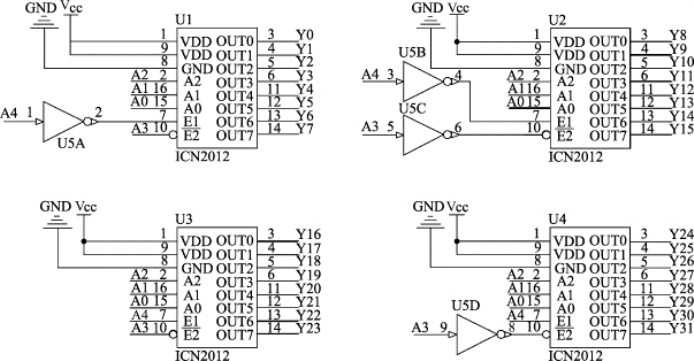

使用单独控制的功率管会需要太多的元件数,这里用4片ICN2012集成芯片来构成一组行驱动电路。ICN2012是一款专用的LED 显示屏行驱动芯片,集成有38译码电路及PMOS 功率管,集成防烧功率管、消隐、LED 灯珠保护等功能,每片ICN2012共有8路输出,每路PMOS输出管的导通电阻为100mΩ,最大驱动电流可达2A,能很好地满足本章LED 屏的要求。

ICN2012有三个二进制输入位[A2A1A0],其数值在[000],[001],…,[111]之间变化,分别被译码成Y0~Y7输出有效。请注意,输出是高电平有效,即若输入为[000]时,Y0为高电平,输出所需要的LED 行驱动电压,其余7个输出全部为低电平。因此,只要通过给[A2A1A0]加上地址数据,就能确保任意时刻所选定的一行也只有这一行得到供电。

四个ICN2012组合可构成32扫所需的32条行线,因此意味着这四个一组的芯片任一时刻只能有一片可以如上所述根据地址数据产生输出,其他三个芯片不能产生输出。如何做到这一点呢?ICN2012除了上述地址输入与8路驱动输出之外,另有两个使能控制输入![]() ,只有取值为[10]时,译码输出才有效,不然所有输出都被禁止。可见,它们可方便地用于实现多芯片的级联。于是,共使用5根地址线[A4A3A2A1A0],[A4A3]用来选择4片ICN2012中的一片使之输出有效,[A2A1A0]直接与ICN2012地址线连接。外加一片74HC04反向器电路,就可构成完整的32扫行驱动电路,如图6.3所示。只要单片机控制电路产生[00000]~[11111]地址信号,驱动电路就会分别产生Y0~Y31行驱动电流。

,只有取值为[10]时,译码输出才有效,不然所有输出都被禁止。可见,它们可方便地用于实现多芯片的级联。于是,共使用5根地址线[A4A3A2A1A0],[A4A3]用来选择4片ICN2012中的一片使之输出有效,[A2A1A0]直接与ICN2012地址线连接。外加一片74HC04反向器电路,就可构成完整的32扫行驱动电路,如图6.3所示。只要单片机控制电路产生[00000]~[11111]地址信号,驱动电路就会分别产生Y0~Y31行驱动电流。

图6.3 显示屏的行驱动电路

3.列驱动电路

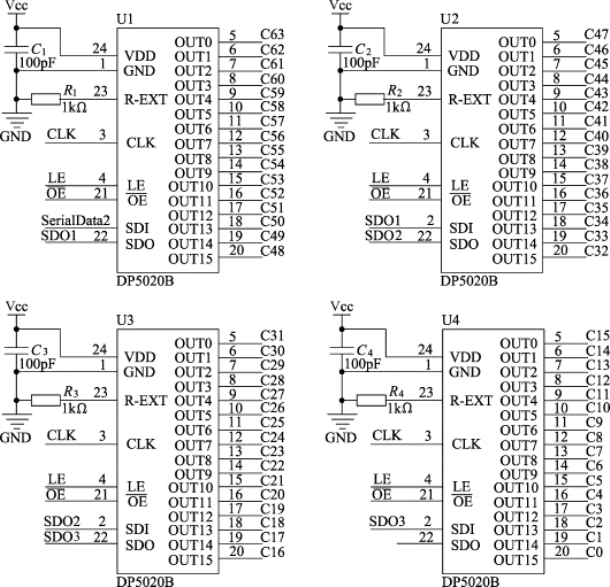

列驱动电路使用LED 显示屏专用恒流源驱动芯片DP5020B,它内建有16 位CMOS位移寄存器与锁存器,可以一次性串行移位输入16位数据并转换成并行输出数据格式,因此可同时驱动16路,并且还能进行级联,即把四片级联,可以一次性移入64位数据。注意到当前应用中每个像素都有RGB 三色,64个像素的每一种颜色都需要4块DP5020B级联,共需要12片才能实现列驱动要求。再考虑到分成上、下两个半屏并行扫描,因此总共需要24片恒流源驱动芯片DP5020B。

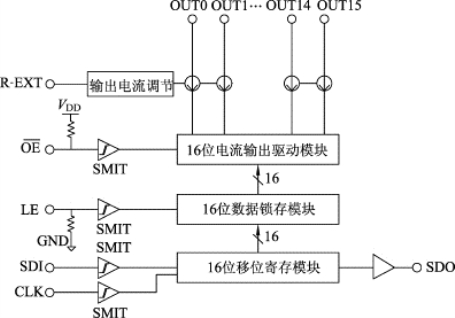

列驱动芯片DP5020B内建有16位移位寄存器、锁存器、输出恒流驱动以及一些辅助控制功能,其基本功能框图如图6.4所示。

图6.4 DP5020B基本功能框图

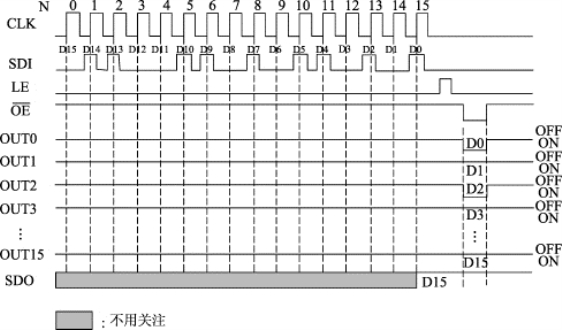

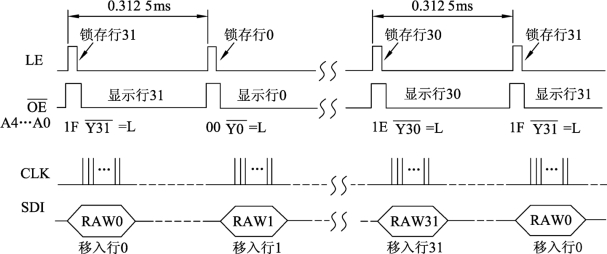

工作过程中,在时钟CLK 控制下,把所要显示的数据通过SDI输入端移入,每个时钟上升沿移入1位,16个时钟之后,全部16位显示数据将进入移位寄存器,注意高位先进,最后移入的一位是与OUT0相对应的。先前移入的数据则会从SDO 移出,级联时只要把前一级SDO 与后一级SDI相连就能实现16位、32位或64位的移位操作。数据高电平有效,输出低电平有效,即移入1,将使对应的OUT 位变低,LED 就可点亮。注意,在进行数据移位时,不会影响当前的输出控制,因此也不会干扰当前LED 显示。只有当移位操作完成并执行寄存器数据向输出锁存器的锁存操作,即在锁存允许引用LE上施加高电平有效的锁存脉冲后,上述数据才能出现在锁存器输出上,即便是这样,它们也不一定会产生输出驱动,除非允许![]() 是低电平。列扫描的完整工作时序如图6.5所示。由于该芯片可以工作在高达25MHz的时钟,因此可以在极短的时间内移入一行的数据,最快只需约0.64μs就可以移入16位的LED 数据。这里的应用例子中,将采用三组RGB数据同时并行移位的方法进行,即RGB三路在同一时钟信号驱动下,同时移入各自的四个相互级联的16位移位寄存器,合在一起构成一行共64个三基色RGB像素数据。因此,完成一行数据的移位最快仅需2.56μs。

是低电平。列扫描的完整工作时序如图6.5所示。由于该芯片可以工作在高达25MHz的时钟,因此可以在极短的时间内移入一行的数据,最快只需约0.64μs就可以移入16位的LED 数据。这里的应用例子中,将采用三组RGB数据同时并行移位的方法进行,即RGB三路在同一时钟信号驱动下,同时移入各自的四个相互级联的16位移位寄存器,合在一起构成一行共64个三基色RGB像素数据。因此,完成一行数据的移位最快仅需2.56μs。

图6.5 显示屏的列扫描时序

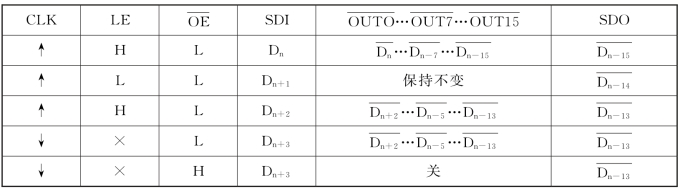

DP5020B芯片真值表见表6.1。从真值表可知,当![]() 为低电平,每当CLK 为上升沿时,SDO 输出为锁存器移出的数据。如上所述,它可用于实现多芯片级联扩展。本章示例因为每一行上有64个列,需要四个16位列驱动电路级联。图6.6给出了一个单色通道64×64 点阵LED 显示屏具体的列驱动电路,其中电路中的[CLK LE

为低电平,每当CLK 为上升沿时,SDO 输出为锁存器移出的数据。如上所述,它可用于实现多芯片级联扩展。本章示例因为每一行上有64个列,需要四个16位列驱动电路级联。图6.6给出了一个单色通道64×64 点阵LED 显示屏具体的列驱动电路,其中电路中的[CLK LE![]() 信号为电路中的所有DP5020B 所共用,用于将控制单片机发来的共有64位的串行数据信号SD 按照时钟信号CLK 的节拍从低位向高位进行移位。由于LED 显示屏的一行有64列,每一片DP5020B有16位输出,需要将一个芯片的串行数据输出管脚SDO 接至下一个芯片的串行数据输入管脚SDI,实现64位的并行输出,需要4片这样的LED 驱动芯片。三个RGB通道的列驱动电路具有完全相同的电路,差别只在于分别接收控制器发过来的RGB移位数据,这三组相同的列驱动电路共用[CLK

信号为电路中的所有DP5020B 所共用,用于将控制单片机发来的共有64位的串行数据信号SD 按照时钟信号CLK 的节拍从低位向高位进行移位。由于LED 显示屏的一行有64列,每一片DP5020B有16位输出,需要将一个芯片的串行数据输出管脚SDO 接至下一个芯片的串行数据输入管脚SDI,实现64位的并行输出,需要4片这样的LED 驱动芯片。三个RGB通道的列驱动电路具有完全相同的电路,差别只在于分别接收控制器发过来的RGB移位数据,这三组相同的列驱动电路共用[CLK![]() 信号。

信号。

表6.1 DP5020B芯片真值表

(www.daowen.com)

(www.daowen.com)

图6.6 显示屏的列驱动电路

这里有一个很重要的映射关系需要明确,图6.6中所示的四块列驱动芯片级联后形成了一个64位的移位寄存器,对应于LED 屏一行上的64列像素。从中可以看出,硬件设计是把每行中64列像素的移位操作按“从右到左”“高位在前”的方式进行的。以第0行为例,首先移入的是图像上第0行第0列的像素,最后一个移入的是第0行第63个像素。这种方式可以简化软件设计,且便于理解,在设计图像帧存与准备图像数据时,可以按实际图像从左到右、从上到下的次序来准备与存取数据,不容易出错。

此外,需要指出的是,DP5020B中R-EXT 管脚与地之间可以接入一个外接电阻来改变整体的显示亮度。接入的亮度调节电阻阻值越大,输出通道OUT0~OUT15的输出电流越小,相应的驱动能力越弱,LED 的亮度越弱。

最后给出1/32行扫描实现全屏幕64×64个LED 动态驱动总的时序。根据前面行驱动电路所描述,将显示屏分为上、下两部分,0~31行、32~63行同时进行行扫描。根据人眼的感受,帧刷新频率要大于等于75Hz,人眼才不会明显感觉画面闪烁。实例中采用的帧刷新频率为100Hz,则帧扫周期为Tf=10ms;由于采用的是1/32的动态扫描,可以求得行扫周期Tr=Tf/32=0.312 5ms。显示屏的行扫描时序如图6.7所示。

图6.7 显示屏的行扫描时序

4.控制器接口

前面描述的行、列扫描均由控制器产生信号并控制完成。显示模块控制器可以用很多方法实现,比如单片机、FPGA 等,本实例选择了STM32F103 单片机作为控制器。

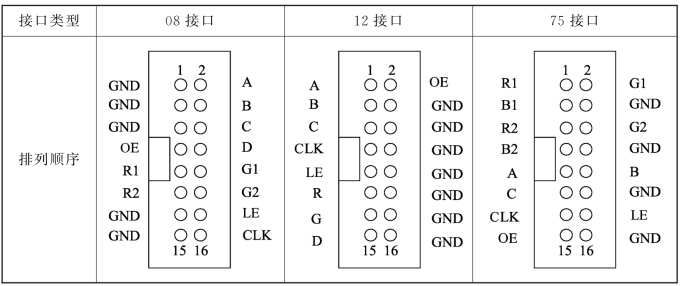

通常市场上购买的通用LED 模组中的行、列驱动电路由LED 显示屏生产厂家集成到面板上,控制器则可以根据实际用户的不同需求自行定制,所以LED 模组一般会提供两个标准的控制接口:输入控制端口与输出控制端口。输入控制端口用于从控制器接收控制、时钟及像素移位数据等信号。所有这些信号通常都会经过总线缓冲后在输出控制端口上复现。这样的设计便于把多个模组拼接,控制信号可以在模组间传递。表6.2给出了目前常见的一些LED 模块控制接口的名称和定义,特别需要注意它们与前面讲述的行扫驱动的5条行选地址线[A4 A3 A2 A1 A0]、列扫驱动中的控制线![]() 以及移位数据线SDI之间的对应关系。只要能够理解这些信号与不同厂家生产模块采用的接口之间的对应关系,设计LED 屏应用系统就会变得比较简单了。

以及移位数据线SDI之间的对应关系。只要能够理解这些信号与不同厂家生产模块采用的接口之间的对应关系,设计LED 屏应用系统就会变得比较简单了。

需要指出的是,不同生产厂家的LED 显示屏虽然使用同种类型的接口,它们一般都会包含必需的通用管脚定义。有些厂商的模块如果包含特殊功能,就会使用那些通用管脚之外的引脚,这些不被通用接口定义的引脚,如果没有特殊用途,一般都是NC端或GND 端,特定厂家会把其中一些NC端或GND 端转而定义成特殊的控制功能。因此,在实际应用时,需要特别清楚地了解你手上的LED 模块,生产厂家有没有使用通用管脚之外的引脚,以及它们是如何被定义的,不要仅仅关注接口类型。

表6.2 LED模块(单元板)常见接口

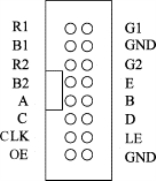

本章将选用75E接口。75E接口是表6.2中75接口的变型。它们的不同之处在于75E接口在75接口的标准定义外做了一些扩充定义,将原接口中的GND 端子赋予了新的定义。75E接口定义图如图6.8所示。其中,R1、G1、B1对应的是64×64显示屏的第0行~第31行动态扫描所对应的红、绿、蓝三色的串行数据,R2、G2、B2对应的是64×64显示屏的第32行~第63行动态扫描所对应的红、绿、蓝三色的串行数据。[E D C B A]是1/32行扫对应的行地址线,分别对应于前面讨论中的[A4 A3 A2 A1 A0],![]() 是列驱动电路所需的控制信号,与之前的讨论保持一致。考虑到控制接口引出的信号后面要带的驱动芯片较多,只通过单片机的输出管脚,其驱动能力可能不足,可以在控制接口的前端或后端增加一级总线缓冲器,以保证电路即使把多个LED 模块级联,也具有足够的驱动能力。

是列驱动电路所需的控制信号,与之前的讨论保持一致。考虑到控制接口引出的信号后面要带的驱动芯片较多,只通过单片机的输出管脚,其驱动能力可能不足,可以在控制接口的前端或后端增加一级总线缓冲器,以保证电路即使把多个LED 模块级联,也具有足够的驱动能力。

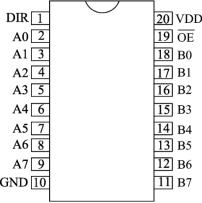

本实例采用8位总线收发器DP74HC245B 来实现上述总线缓冲,该芯片是一款三态输出、八路信号双向收发器,有两个控制端![]() 。其中,DIR 为数据流向控制端,_当DIR 为高电平时,数据流向为A→B;当DIR 为低电平时,数据流向为B→A。

。其中,DIR 为数据流向控制端,_当DIR 为高电平时,数据流向为A→B;当DIR 为低电平时,数据流向为B→A。![]() 为输出状态控制端,高电平时,输出为高阻态;低电平时,数据正常传输。其芯片管脚定义图如图6.9所示。

为输出状态控制端,高电平时,输出为高阻态;低电平时,数据正常传输。其芯片管脚定义图如图6.9所示。

图6.8 75E接口定义图

图6.9 DP74HC245B芯片管脚定义图

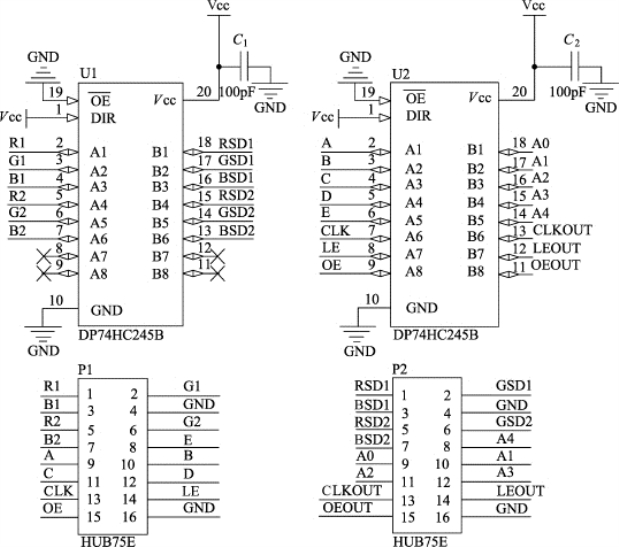

由于图6.8所示的75E接口中存在两组RGB数据线,共6条,[E D C B A]地址线共5条,外加![]() 控制线3条,合计14条信号线需要进行缓冲,使用两片DP74HC245B即可满足需要。具体的接口驱动电路如图6.10所示。

控制线3条,合计14条信号线需要进行缓冲,使用两片DP74HC245B即可满足需要。具体的接口驱动电路如图6.10所示。

图6.10 接口驱动电路

有了上述完整的电路设计后,接下来的任务是让驱动系统中的控制器产生所有扫描所需的地址、数据以及控制信号。本实例中,所有这些信号都是由STM32 单片机,在软件系统的控制下,准确地产生它们。下一节将讨论控制器的软件设计。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。