1.可测试性设计

可测试性设计(Design For Test,DFT)如图8.4所示。

图8.4 CP测试工艺流程

2.选测试厂,测试机

测试厂和测试机的选择要考虑芯片类型、测试内容、测试规格和成本等因素。

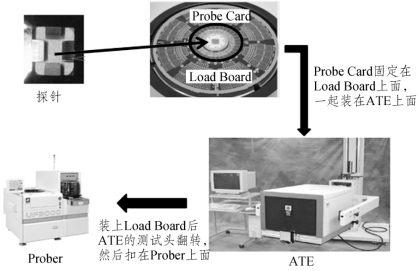

ATE由机台(Tester)、载板(Load Board)、探针卡(Probe Card)、分选机(Handler)和测试软件等部分组成。CP测试自动测试机上不需要Load Board和Handler。ATE机器如图8.5所示。

图8.5 ATE机器

按照侧重的芯片类型和测试内容,测试机台有很多品牌和产品系列。

3.制作Probe Card以及Test Program

选择好测试机后,硬件方面需要制作Probe Card,软件方面需要制作Test Program。

Probe Card是探针卡。Probe Card制作前的准备工作:

(1)选ATE和Prober。Prober厂家有TEL、TSK、EPSON,国内装机比较多的是TEL-P8、P12、TSK-UF200、UF3000。

(2)同测数和芯片PAD的坐标数据。

(3)Load Board和Probe Card制作厂家的选择。

Probe Card的制作厂家有:① 日本厂家JEM、MMS(旺杰芯);② 美国厂家PROBER LOGIC、KNS、CASCADE;③ 中国厂家Probeleader、上海菁成、圣仁,上海依然,江阴JCAP。

根据针的数目、PAD的尺寸和间距来选择合适的厂家,一般都能做到10 μm精度,但是5 μm以下的精度就要选择比较好的厂家。(www.daowen.com)

(4)探针材质选择。

钨针:优点是成本低、硬度/抗疲劳性佳、寿命长;缺点是易粘异物或化学物质造成阻抗增加,且不适用高电流测试。

铼钨针:优点是硬度/抗劳性佳,稳定度佳适合长时间测试;缺点是接触电阻成本较高。

BeCu针:优点是接触电阻较不易粘异物;缺点是易秏损,弹性较差。

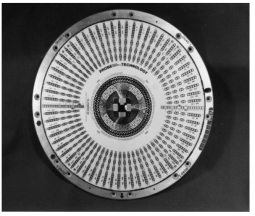

(5)Probe Card包括探针和芯片外围电路。裸DIE规则地布满整个Wafer,无论哪片Wafer,每颗Die都有固定的位置,芯片管脚的位置也就固定。这些位置坐标和间距都信息在芯片投产前已经确定,制作针卡需要这些参数。探针有钨铜、铍铜或钯等材料,这些探针在强度、导电性、寿命、成本等方面各有特点。

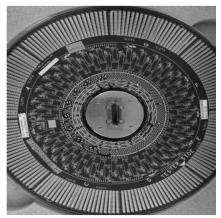

针卡还需要确定同测数(Site)。增加同测数可以节约测试机时成本,但是受限于测试机台资源,同测数有上限,例如32/16/8/4。自动测试探针如图8.6所示。Probe Card如图8.7所示。

图8.6 自动测试探针

图8.7 Probe Card

(6)编写测试程序(Test Program)。测试程序控制整个机台的测试过程。不同的测试机有不同的测试软件系统,对应的测试程序也有不同的格式。通常工程师提供WGL/STIL/VCD等格式的文件,再转换成测试机需要的文件格式,并增加其他测试程序。

4.调试以及结果分析

Wafer由Foundry出厂转运至测试厂,ATE软硬件就绪后就可以开始进行调试了。

根据测试计划,Pattern(测试向量)被分作不同的Bin,从而定位测试错误的位置。调试时还可以在系统上直接看到一个Pattern中错误的Cycle(环)位置,工程师根据这些错误信息进行调试(debug),修改Pattern和测试程序,逐个清理,直到所有Bin都通过。

同测的多Site(点)全部Pass并循环多轮后,便可以在整片Wafer上Try Run(试运行)。此时工程师还要调试探针力度、清理探针周期等参数,确保整片Wafer上每一次Touchdown(向下扎针)都可以测试稳定。

整片Wafer的测试结果通常生成一个WaferMap文件,数据生成一个datalog,例如STD文件。WaferMap主要包含良率、测试时间、各Bin的错误数和Die位置,datalog则是具体的测试结果。工程师通过分析这些数据,决定是否进入量产。

5.量产CP测试

进入量产阶段后,根据大量测试的统计数据,可以进行一些调整以进一步优化测试流程。根据结果将错误率较高的Bin尽量排在靠前的位置,测试进行到第一个出错的Bin后就不再继续向下进行,以节省测试时间,并且防止已发现的错误导致后续测量损坏针卡。将错误率较低的Bin排在靠后的位置,当错误率极低时,甚至删除该测试,以节省测试时间。决定是否对出错的Die进行复测。由于各种原因,对于出错的Die,再重新测试一次。通常复测可以纠正一定比例的错误,但是要多用一部分测试时间,所以要综合考虑决定是否复测。通常处于Wafer边缘位置的Die出错的概率较高,综合考虑,有时可以直接将边缘Die剔除,不进行测试就标为坏品,以节省测试时间。还需要关注良率是否稳定,当连续出现良率较低的情况时,需要停止测试,进行数据分析,检查设备或与Foundry沟通。量产CP测试的结果需要交给后续封装厂使用。通常是一个含有分Bin信息的Map文件,封装厂根据Map文件挑选好品封装,剔除坏品,还可以保留客户选择的特殊Bin类别。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。