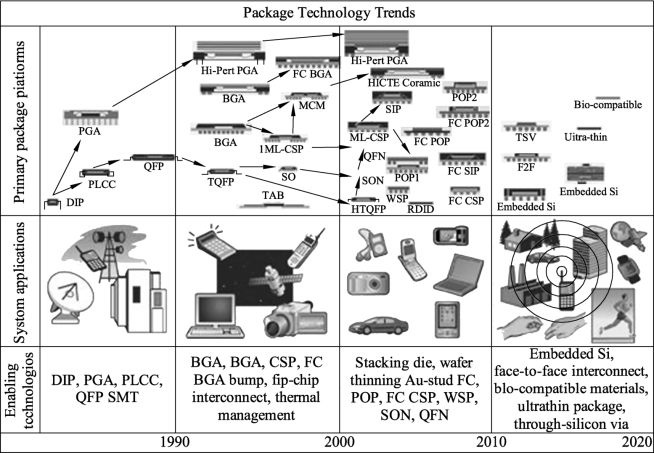

随着电子产品在个人、医疗、家庭、汽车、环境和安防系统等领域得到广泛应用,同时在日常生活中更加普及,人们对新型封装技术和封装材料的需求变得愈加迫切。电子产品继续在个人、医疗、家庭、汽车、环境和安防系统等领域得到新的应用。为获得推动产业向前发展的创新型封装解决方案(见图7.36),在封装协同设计、低成本材料和高可靠性互连技术方面的进步至关重要。

图7.36 封装技术的发展趋势也折射出应用和终端设备的变化

在众多必须解决的封装挑战中,需要强大的协同设计工具的持续进步,这样可以缩短开发周期并增强性能和可靠性。节距的不断缩短,在单芯片和多芯片组件中三维封装互连的使用,以及将集成电路与传感器、能量收集和生物医学器件集成的需求,要求封装材料具有低成本并易于加工。为支持晶圆级凸点加工,并可使用节距低于60 μm凸点的低成本晶圆级芯片尺寸封装(WCSP),还需要突破一些技术挑战。最后,面对汽车、便携式手持设备、消费和医疗电子等领域中快速发展的MEMS(微机电系统)器件带来的特殊封装挑战,我们也要有所准备。

1.封装设计和建模

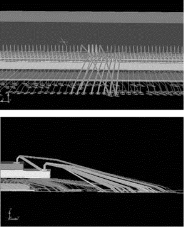

建模设计工具已经在电子系统开发中得到长期的使用,这包括用于预测基本性能,以保证性能的电学和热学模型。借助热机械建模,可以验证是否满足制造可行性和可靠性的要求。分析的目标是获得第一次试制时就达到预期性能的设计。随着电子系统复杂性的增加以及设计周期的缩短,更多的注意力聚焦于如何将建模分析转换到设计工程开始时使用的协同设计工具之中,优化芯片的版图和架构并进行必要的拆分,以最低成本的付出获得最高的性能。复杂的芯片叠层和互连建模如图7.37所示。

图7.37 复杂的芯片叠层和互连建模

2.互 连

传统的互连选择包括在成本敏感的高性能应用中的引线键合和焊球倒装芯片。随着电子产业更加转向消费类产品,即使对于高性能产品,成本也变得更加重要。消费类产品所需的便携性也增加了对尺寸的要求,推动了引线键合以及焊球倒装芯片互连节距的降低,也为新型互连技术的发展提供了动力。在某些情况下节距低于150 μm,传统的焊料凸点倒装芯片互连已不能提供足够的可制造性或可靠性,除了尺寸最小的芯片外。芯片与衬底的支起高度已经达到或低于凸点的半节距,影响了倒装芯片器件的可制造性和可靠性。在一些临界值下,由于邻近凸点以及芯片与衬底表面构成的通道非常小,芯片下填充物流动的阻力超过了毛细管效应提供的动力。

图7.38 互连凸点

3.材 料

新材料推动不同的工艺相互作用,并改变互连、界面和可靠性等对应的物理特性。举例来说,在键合中转而使用铜线将带来新的现象,必须进行相应研究和表征。绿色材料的引入大大影响了引线框架封装的可制造性、成本以及可靠性。其他的一些因素,包括汽车发动机腔体的高温环境,高电压(500~1000 V)需求,用于高功率IC的高导电率芯片粘结材料,以及用于高电流承载的厚导体。在引线框架、模塑混合物和互连线中使用的传统材料的替代品正在出现,这包括铝引线框架、无金丝互连,以及与超薄芯片一起使用的低成本注模技术。

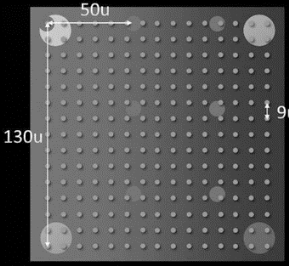

4.窄节距凸点技术

部分游戏和无线领域使用或者正在考虑使用凸点节距低于60 μm的倒装芯片封装,而标准的凸点节距为150 μm。逐渐被采用的潜在解决方案包括缩小凸点的尺寸或者使用顶部覆盖一层焊料的较厚的钉头(Stud)来提供芯片与衬底间的支撑高度。节距更密集的凸点以及提高电镀铜厚度的可能性为该领域材料和工艺的选择带来挑战和机遇。对于通过电镀制作的凸点而言,首先面临的挑战是光刻胶材料的选择。制作这种节距范围的凸点,需要进行受控电镀,而非快速扩散的电镀,需采用较厚的光刻胶,高宽比可能超过3∶1。采用正性和负性光刻胶都可以得到所需的厚度。正性光刻胶具有易控制形状和去胶方便的优势,而负性光刻胶具有易控制曝光能量和显影时间的优势。目前为止,选用的光刻胶已经可以将高宽比做到4∶1,仅就图形的高宽比而言,已经得到了比预期更突出的能力。在化学浸润高的高宽比结构方面,一些材料表现出较强的能力或挑战。

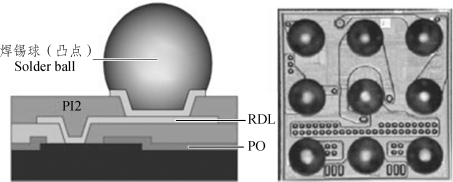

5.WCSP

晶圆级芯片尺寸封装(WCSP)应用范围在不断扩展并进入新的领域,而且根据引脚数目和器件类型细分市场。无源器件、分立器件、RF和存储器件的份额不断提高,并开始进入逻辑IC和MEMS之中。随着芯片尺寸和引脚数目的增加,板级可靠性成为一大挑战。在过去的十年间,低引脚数目的WCSP部分已经变得非常成熟,众多厂家使用不同尺寸的晶圆不断推出高产量应用,并不断扩展面向不同市场的产品空间。随着基础设施建立的完成,并且也已经实现量产,下一个主要聚焦的方面是降低成本,这对于低引脚数目的器件来说尤为关键,同时对高数目引脚的器件来说也很重要,包括300 mm晶圆。SiP技术已经开始集成MEMS器件,以及其他的一些逻辑和面向特定应用的电路。MEMS应用覆盖了惯性/物理、RF、光学和生物医学等领域,而且这些应用要求使用不同种类的封装,比如开腔封装、过模封装、晶圆级封装和一些特殊类型的密闭封装。这些微系统必须具备可以在潮湿、盐渍、高温、有毒和其他恶劣环境中工作的能力。扇出技术WCSP结构如图7.39所示。

图7.39 扇出技术WCSP结构

降低封装成本是MEMS器件面临的最大挑战,而这推动着更多的标准化和封装在填充因子方面通用性的发展。其他的一些关键性挑战包括应力管理(特别是对于压力和惯性传感器)、避免污染杂质、组装位置偏差、压力控制以及密闭性等。

6.芯片规模封装(CSP)

20世纪90年代末期,随着信息化步伐的加快,移动通信手机、掌上计算机、数码相机等手持产品的普及,以及真正意义上多媒体时代的到来,人们一直在寻找着更轻、更薄、更紧凑、更低成本,同时又有良好的电气性能,以及高速、高可靠、高封装密度、易于工业自动化大生产新的封装技术和封装形式,因此芯片封装进入了飞速发展时期。

CSP以其成熟的工艺、较低的制造成本、便利而又最有发展潜力的封装形式诞生,并在高密度微电子封装技术领域占有一席重要的位置。CSP是在BGA基础上发展起来的,被业界称为单芯片的最高形式,其定义为封装面积不大于1.2倍芯片尺寸的一种封装。

由于CSP封装的面积大致和芯片一样,它大大节约了印制电路板的表面积。其外引线为小凸点或焊盘,既可四周引线,也可以底面上阵列式布线,引脚间距为0.5 mm、0.75 mm、1.0 mm。通常把CSP分为四种类型:即刚性基片类、柔性电路垫片类、引线框架类和晶圆片级组装类。

CSP和BGA很容易区分,球间隔小于1.0 mm的封装为CSP,球间隔大于或等于1.0 mm的封装为BGA。CSP封装可以让芯片面积与封装面积之比超过1∶1.14,已经相当接近1∶1的理想情况,绝对尺寸也仅有32 mm2,约为普通BGA的1/3,仅仅相当于TSOP内存芯片面积的1/6。它体积小,是目前为止体积最小的封装LSI,相同尺寸的LSI其引脚最多。CSP是实现高密度化、微型化安装较为理想的新技术。

上述的诸多优点使它成为目前和今后最具优势的高密度电路组装方法之一。但因其制作工艺复杂,同时对材料的匹配性及监测设备的要求较高,其造价要高于相应的BGA产品。随着相关技术问题的解决,CSP会逐渐走向成熟,将成为封装技术革新的主流和未来贴装型IC之星。

结论:先进封装在推动更高性能、更低功耗、更低成本和更小形状因子的产品上发挥着至关重要的作用。在芯片封装协同设计以及为满足各种可靠性要求而使用具成本效益的材料和工艺方面,还存在很多挑战。为满足当前需求并使设备具备高产量大产能的能力,业界还需要在技术和制造方面进行众多的创新研究。在能量效率、医疗护理、公共安全和更多领域,都需要创新的封装解决方案。

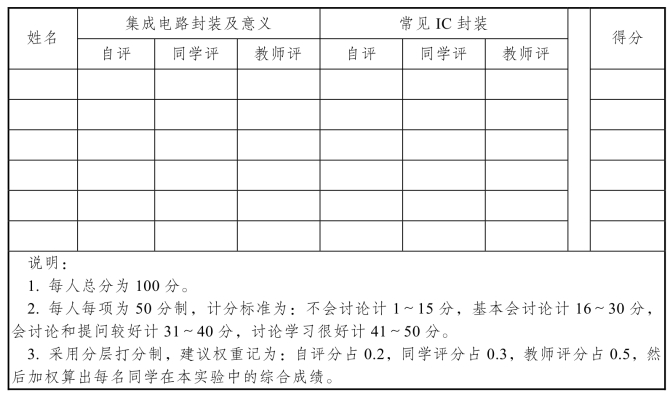

任务三学习成果评价

以团队小组为单位完成任务,以学生个人为单位实行考核。

本模块知识小结

本模块主要介绍了集成电路封装,及其作用与意义;详细介绍了FOL前段工艺,有晶圆背面减薄,晶圆划片,芯片粘接,芯片互连技术;也详细介绍了EOL后段工艺,它包括注塑、激光打字、去飞边和毛刺、电镀、切筋成型等工艺;最后详细介绍集成电路典型封装(如BGA,CSP等)和封装技术发展方向。通过本模块学习可使读者掌握较详细的集成电路封装知识,可为读者学习后续IC测试的内容奠定基础。

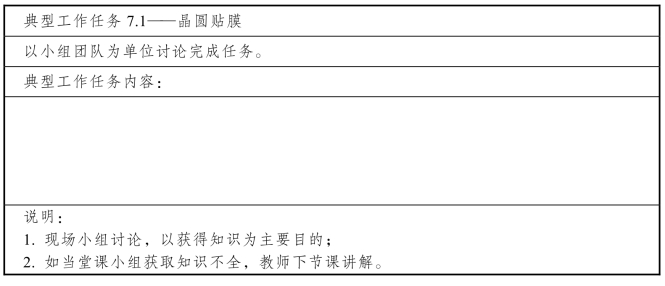

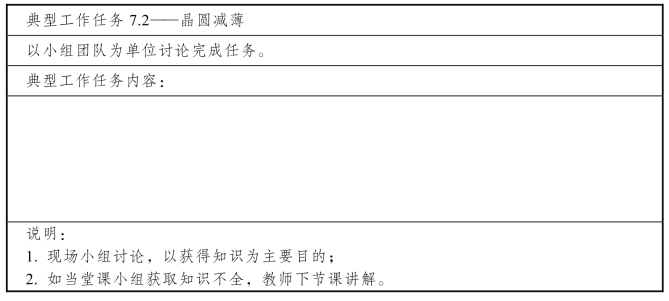

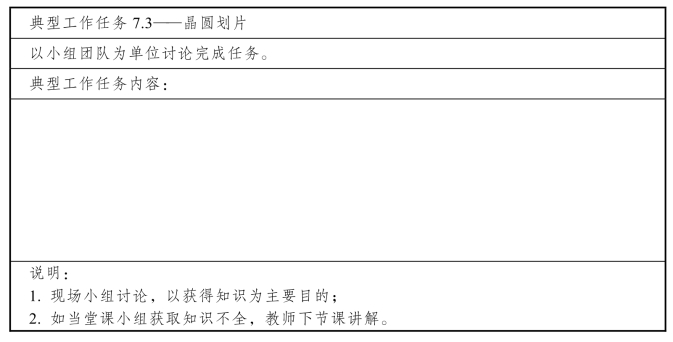

现场典型工作任务案例教学

模块七测评题

一、名词解释

1.切筋;(www.daowen.com)

2.成型;

3.三种芯片的引线键合技术;

4.晶圆切割;

5.CD。

二、填 空

三、简 答

1.简述载带自动焊的关键技术。

2.简述CSP的封装技术。

3.简述BGA和CSP的封装比较。

4.简述封装中涉及的主要材料。

5.简述引线材料。

6.简述引线框架材料。

7.简述芯片粘结材料。

8.简述模塑料。

9.简述焊接材料。

四、选择题

1.英制0805组件长、宽为( )。

A.2.0 mm、1.25 mm B.0.08 inch、0.05 inch

C.二者皆是 D.以上皆非

2.锡膏板从贴完片到过完炉之间的时间不大于( )。

A.1小时 B.2小时

C.3小时 D.4小时

3.型号为SAC305之锡膏要求其存贮温度为( )。

A.5~10 °C B.3~7 °C

C.10~28 °C D.55%~65%RH

4.对于不能立即消耗的潮湿敏感器件,应该( )。

A.由SMT物料员按正常物料集中管理

B.SMT物料员负责烘烤后,按正常物料集中管理

C.SMT物料员负责烘烤后真空包装,按正常物料集中管理

5.CHIP组件的发展趋势为( )。

a.0201 b.1005 c.0603

d.2012 e.1206

A.e→d→c→b→a B.a→b→c→b→e

C.d→e→c→b→a D.a→b→c→d→e

6.瓷片电容的表面上标示“103”,其参数为( )。

A.100 pF B.10 nF

C.100 nF D.10

模块七学习总结报告

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。