【摘要】:晶圆减薄,是对制作集成电路中的晶圆体减小尺寸,为了制作更复杂的集成电路。这一工艺过程称之为晶片背面减薄工艺,简称晶圆减薄,对应装备就是晶片减薄机。图7.4晶圆减薄与蓝膜常规工艺:将从晶圆厂出来的Wafer进行背面研磨来减薄晶圆,达到封装需要的厚度;磨片时,需要在正面贴胶带保护电路区域同时研磨背面。

晶圆减薄,是对制作集成电路中的晶圆体减小尺寸,为了制作更复杂的集成电路。从集成电路断面结构来看,大部分集成电路是在硅基体材料的浅表面层上制造。由于制造工艺的要求,对晶片的尺寸精度、几何精度、表面洁净度以及表面微晶格结构提出很高要求,因此在几百道工艺流程中,不可采用较薄的晶片,只能采用一定厚度的晶片在工艺过程中传递、流片。通常在集成电路封装前,需要对晶片背面多余的基体材料去除一定的厚度。这一工艺过程称之为晶片背面减薄工艺,简称晶圆减薄,对应装备就是晶片减薄机。

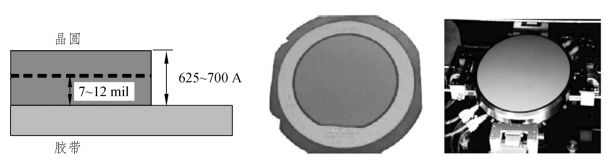

作用:通过减薄/研磨的方式对晶片衬底进行减薄,改善芯片散热效果。减薄到一定厚度有利于后期封装工艺。晶圆减薄与蓝膜如图7.4所示。

(www.daowen.com)

(www.daowen.com)

图7.4 晶圆减薄与蓝膜

常规工艺:将从晶圆厂出来的Wafer进行背面研磨来减薄晶圆,达到封装需要的厚度(8~10 mils);磨片时,需要在正面(Active Area)贴胶带保护电路区域同时研磨背面。研磨之后,去除胶带,测量厚度;将晶圆粘贴在蓝膜(Mylar)上,使得即使被切割开后,不会散落;通过Saw Blade将整片Wafer切割成一个个独立的Die(晶粒),方便后面的Die Attach(芯片粘接)等工序。Wafer Wash(晶圆清洗)主要清洗Saw时候产生的各种粉尘,清洁Wafer;减薄/抛光到80~100 μm,粗糙度为5~20 nm,平整度为±3 μm。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。

有关现代集成电路制造工艺的文章