半导体的掺杂(Doping)技术是将一定数量和一定种类的杂质掺入硅中,并获得精确的杂质分布形状(Doping Profile)。掺杂应用于MOSFET的阱、栅、源/漏、沟道等。掺杂目的是改变晶片电学性质,实现器件和电路纵向结构。

半导体的常用掺杂技术主要有两种,即高温(热)扩散(Diffusion)和离子注入(Ion Implantation)。一直到20世纪70年代,杂质掺杂主要是由高温扩散方式来完成,杂质原子通过气相源或掺杂过的氧化物扩散或淀积到硅晶片的表面,这些杂质浓度将从表面到体内单调下降,而杂质分布主要是由高温与扩散时间来决定。

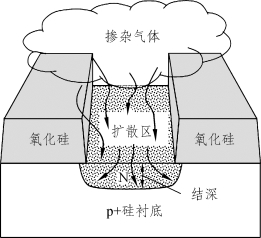

掺入的杂质主要有两类:第一类是提供载流子的受主杂质或施主杂质(如Si中的B、P、As);第二类是产生复合中心的重金属杂质(如Si中的Au)。离子注入中掺杂离子以离子束的形式注入半导体内,杂质浓度在半导体内有个峰值分布,杂质分布主要由离子质量和注入能量决定。扩散和离子注入两者都被用来制作分立器件与集成电路,二者互补,相得益彰。硅衬底掺杂如图6.17所示。

图6.17 硅衬底掺杂

掺入的杂质是电活性的,能提供所需的载流子,使许多微结构和器件功能得以实现。掺杂的最高极限约1021个/cm3(原子个数),最低1013个/cm3硅。

1.受主杂质

当在半导体材料(例如硅)中人为地掺入价电子数更少的杂质原子,例如硼,来取代晶格中硅原子的位置,杂质原子缺少电子与硅形成共价键,需要从别处的硅原子夺取一个价电子,形成空穴和负电中心,这种掺入的杂质元素称为受主杂质(又称P型杂质)。(https://www.daowen.com)

常见杂质有B、Al、Ga、In等。以硅晶体中掺入硼为例来说明受主杂质的作用。一个硼原子占据了硅原子的位置,硼原子有三个价电子,当它和周围的四个硅原子形成共价键时,还缺少一个电子,必须从别处的硅原子中夺取一个价电子,于是在硅晶体的共价键中产生了一个空穴。而硼原子接受一个电子后,成为带负电的硼离子(B-),称为负电中心。负电中心对空穴的束缚较小,只需要很少的能量空穴就可以挣脱束缚,称为自由运动的导电空穴。因为杂质可以在硅、锗中能够接受电子产生导电空穴,并形成负电中心,所以称它们为受主杂质或P型杂质。掺杂结果:纯净的半导体中掺入受主杂质后,受主杂质电离,使价带中的导电空穴增多,增强了半导体的导电能力,通常把主要依靠空穴导电的半导体称为空穴型或P型半导体。

2.施主杂质

为了控制半导体的性质,可以人为地掺入某种化学元素的原子,掺入杂质元素与半导体材料价电子的不同而产生的多余价电子会挣脱束缚,成为导电的自由电子,杂质电离后形成正电中心,称这些掺入的元素为施主杂质(又称N型杂质)。常见杂质P、As、Sb的掺杂方式:以半导体材料硅为例,杂质原子进入半导体硅后,只可能以两种方式存在。一种方式是杂质原子位于晶格原子间的间隙位置,常称为间隙式杂质;另一种方式是杂质原子去掉晶格原子而位于晶格格点处,常称为替位式杂质。

原理:以硅中掺杂磷(P)为例,一个磷原子占据了硅原子的位置,磷原子有5个价电子,其中4个价电子与周围的4个硅原子形成共价键,还剩余一个价电子。同时磷原子所在处也多了一个正电荷+q(硅原子去掉价电子有正电荷4q,磷原子去掉价电子有正电荷5q),称这个正电荷为正电中心磷离子(P+)。所以磷原子替代硅原子后,其效果是形成一个正电荷中心P+和一个多余的价电子。这个多余的价电子就束缚在正电中心P+的周围。但是,这种束缚作用比共价键的束缚作用弱得多,只要很少的能量就可以使它挣脱束缚,成为导电电子在晶格中自由运动。掺杂结果:在纯净半导体中掺入施主杂质,杂质电离以后,导带中的导电电子增多,增强了半导体的导电能力。通常把主要依靠导带电子导电的半导体称为电子型或N型半导体。

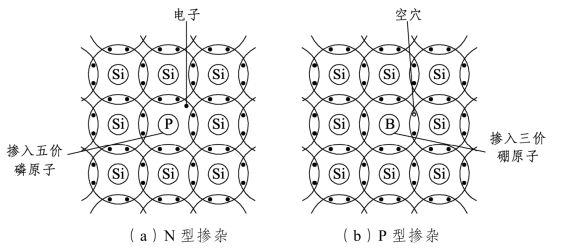

N和P型掺杂如图6.18所示。

图6.18 N型和P型掺杂

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。