化学气相沉积法定义为化学气相反应物,经由化学反应,在基板表面形成一非挥发性的固态薄膜。对于一种或数种物质的气体,以某种方式激活后,在衬底表面发生化学反应并淀积出所需固体薄膜的生长技术。其英文原名为Chemical Vapor Deposition,简称为CVD。注意:化学反应不是发生在气体与衬底之间的,CVD工艺一般用于介质层和半导体材料的薄膜制备,是最常在半导体制程中使用的技术。

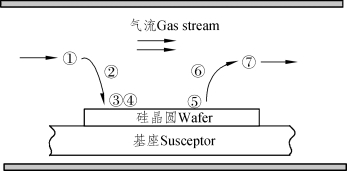

通常化学气相沉积法包含有下列7个步骤(见图4.12):

图4.12 CVD7个步骤

(1)反应剂分子以扩散方式从气相引导到晶片衬底附近。

(2)反应剂分子通过边界层转移到晶片衬底表面。

(3)晶片衬底表面吸附反应剂分子。

(4)反应剂分子在硅衬底表面扩散、积累并完成化学反应,形成薄膜层。

(5)残余反应剂分子和副产品从表面解析。

(6)解析的残余反应剂分子和副产品从表面转移。

(7)残余反应剂分子和副产品以扩散方式转移到气相,随气流排出。

在实际的应用中,当化学反应仅在硅片表面处发生并形成固体时,称该反应为异质过程(Heterogeneous Process),当化学反应是在腔内气体中自发发生(与位置无关)时,称该反应为同质过程(Homogeneous Process),而异质间反应是我们所想要的,因为这样的反应只会选择性在有加热的基板上发生,而且能生成品质好的薄膜。相反地,同质反应就不是我们想要的,因为它们会形成欲沉积物质的气相颗粒,造成很差的黏附性及拥有很多的缺陷,且密度低的薄膜。此外,如此的反应将会消耗掉很多的反应物而导致沉积速率的下降。因此在化学气相沉积法的应用中,一项很重要的因素是异质间反应远比同质反应易于发生。

最常用的化学气相沉积法有常压化学气相沉积法(Atmospheric Pressure CVD,APCVD)、低压化学气相沉积法(Low Pressure CVD,LPCVD)和等离子增强化学气相沉积法(Plasma Enhanced CVD,PECVD),而这三种化学气相沉积法均有各自的优缺点及应用的地方。低压化学气相沉积法拥有很均匀的阶梯覆盖性,很好的组成成分和结构的控制,很高的沉积速率及输出量,以及很低的制程成本。再者低压化学气相沉积法并不需要载子气体,大大降低了颗粒污染源。因此低压化学气相沉积法被广泛地应用在高附加价值的半导体产业中,用以做薄膜的沉积。在硅的成长过程中,使用低压的目的在于减小自掺杂(来自基板本身的杂质)的效应,而这正是常压化学气相成长的最主要问题。在未来元件尺寸越做越小的情况下,制程温度必须降低,而低压化学气相沉积法的最严重问题是它的制程温度稍高,而等离子增强化学气相沉积法即是一种合适的方法,可以解决这个问题。化学气相沉积法的反应器的设计和操作,会因不同的要求而不同,因此这些反应器可以不同的方式分类。一种分类法是依对晶片加热的方式来区别,另一种是依反应腔体内的压力来分类(常压或是低压)。对晶片的加热方式可分成以下4类:热阻丝加热方式、射频(RF)感应加热方式、等离子增强(Plasma)加热方式、光能加热方式.

所加的能量可能转换至反应气体本身或是基板上。当使用反应腔体热阻丝线圈加热方式时,除了晶片本身外,反应腔体的炉壁也会被加热,因此如此的设计称作“热壁反应器”(Hot Wall Reactors)。在这种系统中所蒸镀的薄膜,除了会在基板上,也会在炉壁上生成。这意味着如此的设计,必须经常清洗炉管,以避免微尘粒污染。另一方面,借由射频感应或在反应器内装紫外线加热灯管来引入热源,将只会对晶片和晶片的载具加热,而不会对反应腔的炉壁加热,如此的设计称作“冷壁反应器”(Cold Wall Reactors),然而,在一些的冷壁反应器的系统中,还是会发生炉壁被加热的情形,所以就必须以冷却炉壁(通入冷却循环水)的方式来降低或避免在炉壁上反应或沉积薄膜。反应炉管的几何形状由反应压力和热源供应方式严格限制,而且这是影响输出量(throughput)的一个重要因素。因为常压反应器的操作在物质传输限制(Mass Transport Limit)区域,因此它的腔体设计必须使每一片晶片表面有相等的流量。所以晶片绝不会以垂直且彼此非常靠近的方式来放置,而宁可采取平躺水平的方式来放置,但是此种设计有一非常严重的问题,即易被掉落的微尘粒污染。而低压化学气相沉积法的炉管设计不会受到在“物质传输限制”区域内反应的限制,因此它的几何形状可设计成使每批的晶片数达到最大值,晶片可以一片接着一片垂直放置,片与片之间的距离可以只有几毫米,因此几个石英制的晶片载体,加起来可放超过200片的晶片,因为低压化学气相沉积法是操作在表面反应限制(Surface Reaction Limited)区域,因此它的反应器设计必须有很好的沉积温度控制,它的加热器采用三区热阻丝的炉子(3-zone Resistance heated fUrnace),此种加热器能提供一稳定且均匀的加热源。在集成电路高产量的需求下,在同一个制程中,每批所能生产的晶片数越多越好。因此就会有如图4.13(a)所示的热壁、低压化学气相沉积的反应器被制造出来。在这个反应器中,晶片是被放置在与反应气体之气体流垂直方向的圆形横截面石英炉管中,气体被限制在晶片与反应腔炉壁的环状空间中流动而且靠层流的方式到达晶片表面。一般在反应腔内的成长压力为0.1~5.0托耳(1托耳≈133帕),反应的温度从300 °C至900 °C,而气体的流量范围为10~1000 cm3/min。

(1)CVD工艺的主要参数有:

衬底温度:主要影响CVD膜的密度、应力、淀积速率、折射率、腐蚀速率等。

气压(各工艺气体的分压):主要影响CVD膜的均匀性、折射率等。

功率:主要影响CVD膜的应力、折射率等。

流量:主要影响CVD膜的膜厚、均匀性等。

(2)CVD膜的主要参数有:

淀积速率:单位时间内,所淀积的CVD膜厚(Å/min)。

台阶覆盖:Sidewall step coverage(侧台阶覆盖),Bottom step coverage(底部台阶覆盖),Conformality(相似、保角性)。

应力:External stresses(外部应力),Thermal stress(热应力),Intrinsic stress(内部应力),(thickness,dep-rate,dep-temperature,impurities,porosity,etc)(厚度、dep速率、dep温度、杂质、孔隙度等)。

密度(g/cm3):单位体积CVD膜的质量,其主要取决于膜的组分及结构的致密性。

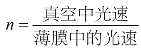

折射率: 。常见材料的折射率如表4.5所示。

。常见材料的折射率如表4.5所示。

表4.5 常见材料的折射率

折射率直接依赖于膜密度。

腐蚀速率:单位时间内,腐蚀掉CVD膜的厚度(Å /min)。

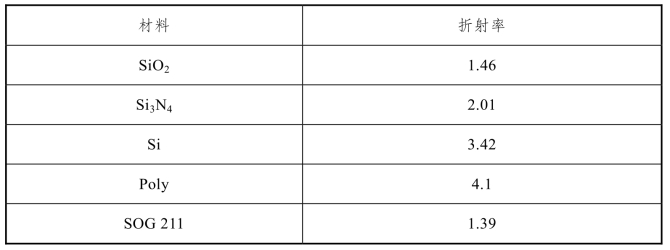

1.常压化学气相淀积

1)APCVD工艺简介

常压化学气相淀积(Atmospheric Pressure CVD,APCVD)是指在大气压下进行的一种化学气相淀积的方法,这是化学气相淀积最初所采用的方法。这种工艺所需的系统简单,反应速度快,但是均匀性较差,台阶覆盖能力差,所以一般用于厚的介质淀积。

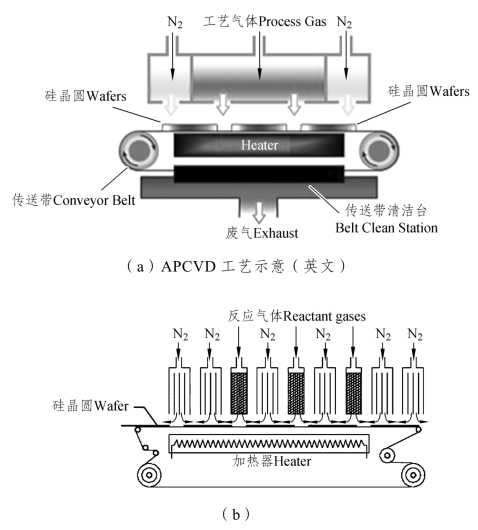

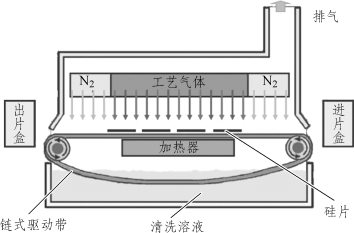

常压化学气相沉积(APCVD)的反应器是第一个被微电子工业所使用的设备,常压下的化学气相沉积反应器很容易设计,并拥有很快的反应速率,但是它对气相反应(Gas-phase Reaction)很敏感,而且它所反应生成的薄膜有很差的阶梯覆盖性(Step Coverage),又因为常压反应器操作在“物质传输限制”区域,所以反应物流必须很均匀地传送至所有基板的每一部分,如图4.13所示。

图4.13 APCVD工艺示意

一般工艺流程:链条式的运载热板做匀速循环运动,片子从设备的一端放入,从另一端取出,经历的是400~500 °C的加热,并有硅烷磷烷和氧气从片子上边喷下反映沉积到片子表面。剩余气体应抽走(反应气体有剧毒)。简单的热CVD反应器如图4.14所示。

图4.14 简单的热CVD反应器

反应方程:

![]()

APCVD最经常的应用是淀积SiO2和掺杂的氧化硅(如PSG、BPSG、FSG等)。传统上这些膜通常作为层间介质(ILD)、保护性覆盖物或者用作表面平坦化。

2)APCVD工艺参数

APCVD工艺中淀积区和外围的非淀积区通常通过流动的惰性气体实现隔离。采取冷壁方式加热,当反应剂为硅烷和氧气系统时,衬底温度在240~450 °C调节。氧气与硅烷气体的流量比为3∶1以上,用氮气作为稀释气体。设备通常采用冷壁式系统,但在常压下反应剂浓度较高,硅烷和氧气的反应仍可能在气相发生,形成硅的氧化物颗粒,这将造成淀积薄膜质量下降,如表面形态差、密度低等一系列问题。通过降低反应剂浓度,添加足够剂量的氮气或其他惰性稀释气体,能够避免气相反应的发生,但这也会降低淀积速率。由于硅烷的氧化温度较低,所以当硅烷和氧在气体喷头处相遇时也会有反应发生,即使这些硅氧化物颗粒生长速率很低,但在淀积了若干衬底硅片以后,颗粒将长大到足以剥落,并落在衬底表面上。因此APCVD工艺的缺点是在制造中会有气相反应形成的颗粒物。

APCVD工艺中,气体反应剂运输区域温度控制比较严格,气相质量输运维持在低温状态,以减少气相中的化学反应发生。而在沉积过程中,薄膜淀积速率对衬底表面反应剂浓度敏感,对衬底温度控制要求不是很严格。设备工作时,反应器衬底温度远高于气流温度,气流的变化会引起衬底温度略有起伏,所以气相运输需要控制衬底温度。所以,APCVD工艺过程中精确控制反应剂成分、计量和气相质量输运过程,对淀积薄膜质量的提高和获得合理的淀积速率起着重要作用。

3)APCVD工艺控制

拉恒温区控制温度:控制在400±10 °C。

颗粒检查:颗粒是AP淀积工艺的大敌,颗粒多就会使腐蚀产生膜的残余,给光刻对位造成影响,严重影响产品质量。我们目前通过使用颗粒度测试仪监控颗粒,规范是颗粒数<200个/0.5 μm。

淀积速率:从膜厚与沉积时间计算得出,这个数值可以直接反映设备内温度或气体比例的变化。在工艺保持不变的条件下,AP的淀积速率不会有太大的变化。WJ999目前的淀积速率是100 Å/min。

均匀性检查:保证硅片中每个芯片和每个硅片的重复性良好,在发现均匀性变差时及时进行调整,一般比较片内与片间均匀性两种,均匀性控制在3 SIGMA以内。

折射率:通过折射率的检查,我们可以通过分析气体的流量以掌握MFC(质流控制器)的状态,使膜的成分保持稳定,确保质量。否则就会使腐蚀时的腐蚀速率难以控制(折射率越大,腐蚀速率越小)。

4)常见问题及处理

(1)APCVD工艺中断对策:根据提示的中断信息,找出中断的真正原因;根据具体情况,确定返工时间的多少。特别注意的是:在返工以前圆片必须经清洗,以防产生颗粒。

(2)APCVD炉管颗粒问题对策:检查排风压力是否在正常范围内。检查环境氮气浮子流量计是否偏离设定值;检查喷网是否老化或者清洗不干净。

(3)均匀性问题对策:检查温度、压力、气体流量等是否正常,否则更换流量计、清洗压力计、重新拉恒温区;可以调整各区的温度、气体的流量、带速以调整均匀性;更换喷网来调整均匀性。

用LPCVD淀积SiO2,常用硅烷和氧反应,反应温度为800 °C左右。

![]()

2.低压化学气相淀积

1)LPCVD工艺简介

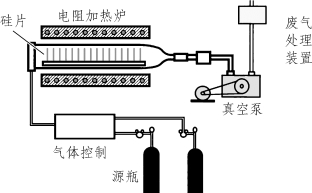

低压气相淀积(Low Pressure CVD,LPCVD)是在27~270Pa的反应压力下进行的化学气相淀积。它的特点是:膜的质量和均匀性好、产量高、成本低、易于实现自动化。

一般工艺流程:装片→进舟→对反应室抽真空→检查设备是否正常→充N2吹扫并升温→再抽真空→保持压力稳定后开始淀积→关闭所有工艺气体,重新抽真空→回冲N2到常压→出炉。

LPCVD工艺流程如图4.15所示。

(https://www.daowen.com)

(https://www.daowen.com)

图4.15 LPCVD工艺流程

2)低压化学气相淀积Si3N4

LPSi3N4在工艺中主要作为局部氧化的掩蔽膜,电容的介质膜等。CMOS工艺最常用的隔离技术就是LOCOS(硅的选择氧化),它以氮化硅为掩膜实现了硅的选择氧化,在这种工艺中除了形成有源晶体管的区域外,其他所有重掺杂硅区上均生长一层厚的氧化层,该厚氧化层通常称为场氧。在工艺中我们通常使用的气体是:NH3+DCS(SiH2Cl2)。这两种气体的反应生成的Si3N4质量高,副产物少,膜厚均匀性极佳,而且是气体源,便于精确控制流量,是目前国内外普遍采用的方法。

反应式方程:

![]()

NH3在过量的情况下,HCl与NH3继续反应:

![]()

合并为

![]()

目前生产使用的温度是780 °C,压力为375 mt。在VLSL(超大规模集成电路)工艺中,由于沿器件有源区方向上的场氧侵蚀和场注入杂质的横向扩散,使得LOCOS(硅局部氧化隔离)工艺受到很大的限制,场氧的横向侵蚀使LOCOS氧化层和栅氧的交界面形成类似“鸟嘴”的结构,随着工艺条宽的不断减少,“鸟嘴”的大小必须加以控制,而Si3N4与硅之间的应力很大,为了避免对硅表面的应力损伤,在硅表面与Si3N4膜之间插入一层薄的SiO2作为应力缓冲层。因此我们常用的方法是通过改变SiN(氮化硅)与二氧化硅的厚度比来减少“鸟嘴”大小,其中“鸟头”的高度和“鸟嘴”的宽度与Si3N4的厚度成反比,与应力缓冲层SiO2的厚度成正比。一般来说该比例越大,“鸟嘴”越小,但比例过大又影响到硅岛侧壁和表面的缺陷密度而引起漏电等不良后果。出于不同工艺要求的考虑,不同公司有各自的做法。最常用的搭配有:200 Å的氧化层+1 175 Å SiN和400 Å的氧化层+1 500 Å SiN,还有很多其他减少“鸟嘴”大小的办法,例如隔离槽填充等。

3)低压淀积多晶硅(LPPOLY)

20世纪60年代作为初期生产的铝栅MOSFET,它的速度、集成度、电源电压与双极电路的兼容性都已无法满足应用的需要,因此开始使用多晶硅薄膜作为自对准绝缘栅场效应晶体管的栅极材料和连接材料。随着集成电路的发展,多晶的应用也越来越广,如用于差值氧化以简化工艺流程,用于负载电阻以缩小电路单元等。

多晶硅薄膜的特性:

(1)多晶硅薄膜的物理和机械特性:多晶硅的结构与掺杂剂或杂质、淀积温度及随后的热处理等因素有密切关系。低于575 °C所淀积的硅是无定形非晶硅;高于625 °C淀积的硅是多晶,具有针状结构;当非晶或针状结构多晶硅经高温退火后,会产生结晶,同时晶粒要长大。多晶硅的晶粒大小与生长温度、多晶硅膜厚及掺杂情况有关。在600~650 °C淀积的多晶硅,具有针状结构,晶粒尺寸在0.03~0.3 μm,具有{110}晶向。多晶硅的腐蚀速率及热氧化速率与掺杂剂浓度有关,腐蚀及氧化的反应速率由掺杂多晶硅的表面自由载流子浓度有关。

(2)多晶硅薄膜的电学性质:多晶硅的电阻率或薄层电阻随淀积温度的增加而降低。多晶硅的电阻率随厚度增加而明显减少,而外延单晶硅的电阻率与厚度无关。

多晶的淀积:600~700 °C化学反应式为:

![]()

影响淀积的主要工艺参量是温度、硅烷流量及反应压力。

目前VTR-2和C-3设备上淀积多晶的条件:

(1)淀积温度:由于LPPOLY的淀积温度限制在600 ~650 °C,因为温度过高,气相反应会生成粗糙,疏松的沉积物,并可能由于硅烷的输送不足使淀积不均匀。在温度低于600 °C时形成的为无定形硅。多晶膜厚随温度的变化较敏感,VTR-2上每变化1 °C,膜厚约变化100 Å左右。生长速率约为94 Å /min。C-3上三温区的淀积速率都为620 °C,温度每变化1 °C,膜厚约变化70~80 Å,淀积速率约70 Å/min。

(2)SiH4流量:多晶硅的淀积速率随SiH4流量的增加而增加,但通常不是硅烷流量的线性函数。这种性质可能是由于质量迁移效应或表面吸附效应所引起。当SiH4浓度过高时,容易出现气相成核,这就限制了硅烷浓度和淀积速率的提高。目前我们淀积多晶硅所使用的是100%的SiH4。VTR-2上的SiH4通过injector管分两路通入,BOTTOM和TOP端各一路,流量分别为125 cc和180 cc;C-3上的SiH4由injector分三路通入,炉管口、炉管中、炉管尾的流量分别为32 cc,48 cc,53 cc。

(3)反应压力:多晶硅的淀积速率随反应压力的增加而加大。目前VTR-2上淀积多晶的反应压力为200 mt,C-3上淀积多晶的反应压力为270 mt。

4)低压沉积

低压沉积(LPTEOS)主要用于SPACER层及电容氧化层。在工艺中,由于注源,漏时杂质的横向扩散会产生短沟道效应,使MOS管的开启电压产生变化,而且高能量的离子注入会令多晶侧壁损伤,因此我们经常使用LDD注入和SPACER层保护来减小短沟道效应的影响和对多晶侧壁的损伤,具体步骤为:在源、漏注入前先进行LDD注入,通常注入浓度为10E+13个/cm3;然后淀积一层LPTEOS;去TEOS,由于台阶的影响,会在多晶侧壁保留有一层TEOS,将起到保护的作用;再开出源、漏的窗口,进行源、漏注入(浓度一般为10E+15个/cm3)。加工时使用的气体为TEOS,也就是Si(OC2H5)4,学名为正硅酸乙酯,又称四乙氧基硅烷,常温下为液态,由携带气体N2带入炉管内,TEOS分压及流量分别由TEOS源瓶的温度及通过源瓶的小N2流量来控制:

![]()

5)LPCVD工艺参数沉积的影响参数

一般而言,因为化学气相沉积的制程,包含了热的传达、边界层的扩散(Boundary-layer Diffusion)、吸附于基板表面、反应物分解、表面扩散、副产物脱离表面等许多步骤,所以有很多个参数会影响沉积作用,如反应温度、压力、反应物流量、晶片摆置的位置和反应物的混合比例都是对是否能沉积出高品质的薄膜非常重要的因素。因为上述的化学气相沉积制程的几个步骤是连续的,哪个步骤是最慢的速率,将会决定此化学气相沉积的速率,亦即是速率决定步骤。速率决定步骤,一般可分成两大类,一类是气相质量输运(Gas-phase Process),另一类是表面反应(Surface Process)。

对于气相质量输运最主要的考量点是反应气体撞击到基板。这个模型要考虑气体横越过边界层(Boundary-layer)的速度,而此边界层就是气体大量流动和基板表面之间的范围。反应物的传输过程是借着气相的扩散来达成,而此气相扩散的速率,正比于扩散系数和横越此边界层的浓度梯度(Concentration Gradient)。因此物质传输的速率受沉积温度的影响比较小。另外,在比较低的沉积温度时,表面反应的速率会降低,最后导致反应物到达的速率比它们因表面反应所消耗的还要多,在这种沉积情况之下,就称为表面反应速率限制(Surface-reaction Limited),反之在比较高的沉积温度下,表面反应速率会提高,最后导致反应物到达的速率远少于因在表面反应所消耗的,在这种沉积情况下,就称为物质传输限制(Mass-transport Limited)。在实际的制程中,从一种限制区域到另外一种限制区域的温度决定于这个反应的活化能(Activation Energy)和在反应器内反应物的流量。

当一个制程在表面反应速率限制的条件下,沉积的温度就是一个很重要的参数,要在整个反应器内有一很均匀的沉积速率,需要有一个能保持固定沉积速率的条件。也就是说,在任何地方,任一片晶片上的表面温度必须保持固定。此外,在这个情况下,反应物到达晶片表面的速度就不是非常重要,因为它们的浓度不会限制沉积的速率,因此它的反应器的设计就没有必要设计成能在每一片晶片上有相等的反应物流量。因此可以看出在低压化学气相沉积系统中,欲沉积的晶片可以垂直摆置,而片与片之间的距离可以很小,那是因为这个系统是操作在表面反应速率限制的模式下。

在低压化学气相沉积法的反应器中,反应压力约为1托耳以下,在此压力下,反应物气体的扩散系数约为在常压下的1 000倍,由于压力降低的调整,因此这净效应使反应物传输至基板表面的速率增加超过10倍,所以速率限制步骤使表面反应。通常表面反应速率会随着表面反应物浓度的增加而增加,以及气相浓度分布不均匀而增加。而气相浓度不均匀是因为某处反应物被空乏掉所造成的,举一个例子说明这个效应,当晶片被放置在靠近反应物的出气端时,因暴露在较低的反应物浓度环境中,比进气端低许多,而造成炉管的前后端沉积的厚度不均匀,因此,为了沉积薄膜的均匀性,在反应炉管的前后两端,沉积的温度必须正确调整。

沉积的制程落在物质传输限制的范围时,制程温度的精密控制就不那么必要,沉积速率的限制和温度的关系也不太有关,另外,在控制反应物于各晶片的摆置点有相等的气体流量是最重要的,因为反应物的到达晶片表面速率,直接正比于反应腔内的浓度梯度,所以要保证在同一片的每个位置有相同的薄膜厚度,反应器在设计时必须使所有晶片的每一点都有相等的反应物流量,因此沉积二氧化硅的常压反应器的,操作温度约为400 °C,落在物质传输限制的区域,所以被应用的反应器设计采用水平摆置晶片的方式,以提供一均匀的气体供应。

6)LPCVD工艺控制

拉恒温区控制温度:定期拉恒温区以得到好的温度控制,保证炉管内各处的生长速率趋向平衡,可以安排一个月拉一次恒温,每次清洗炉管后再拉一次。

颗粒检查:颗粒是LP淀积工艺的大敌,颗粒多就会使腐蚀产生膜的残余,给光刻对位造成影响,严重影响产品质量。目前我们通过使用TENCOR 6420监控颗粒,规范是颗粒数<300个/0.5 μm。

淀积速率:淀积速率从膜厚与沉积时间计算得出,这个数值可以直接反映炉管内压力,温度或气体比例的变化。在工艺保持不变的条件下,LP的淀积速率不太有大的变化。卧式炉目前的淀积速率:LPSIN为30 Å/min;LPTEOS为50 Å/min;LPPOLY为70 Å/min。

均匀性检查:保证硅片中每个芯片和每个硅片的重复性良好,在发现均匀性变差时及时进行调整,一般比较片内与片间均匀性两种,每个星期做一次颗粒均匀性试炉。均匀性控制在3 SIGMA以内。

折射率:通过折射率的检查,我们可以分析LP Si3N4炉管气体的流量掌握MFC的状态,保证膜的成分保持稳定,确保质量。否则就会使腐蚀时的腐蚀速率难以控制(折射率越大,腐蚀速率越小)。

7)常见问题及处理

(1)LPCVD炉管工艺中断。

对策:根据提示的中断信息,找出中断的真正原因;根据具体情况,确定返工时间的多少,将返工时间减去1~2 min,作为气体开关时的补偿。特别注意的是,在返工以前圆片必须经清洗,以防产生颗粒。

(2)LPCVD炉管颗粒问题。

对策:分析测量结果,排除测量的影响;若是Si3N4颗粒,要看颗粒片前是否放了挡片,挡片是否干净;对炉管进行清洗后再做颗粒试炉;检查设备状态,清洗炉管和陪片。

(3)均匀性问题。

对策:检查温度、压力、气体流量等是否正常,如不正常则更换流量计,清洗压力计,重新拉恒温区。

可以调整各区的温度、气体的流量、淀积时间以调整均匀性。

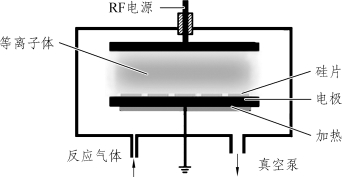

3.等离子体增强化学气相沉积法

等离子体增强化学气相沉积法(Plasma Enhanced Chemical Vapor Deposition,PECVD)借助微波或射频等使含有薄膜组成原子的气体电离,在局部形成等离子体,而等离子化学活性很强,很容易发生反应,在基片上沉积出所期望的薄膜。为了使化学反应能在较低的温度下进行,利用了等离子体的活性来促进反应,因而这种CVD称为等离子体增强化学气相沉积。优点:基体温度低、沉积速率快、成膜质量好、针孔较少、不易龟裂。

一般工艺流程:装片→对反应室抽真空→检查设备是否正常→预淀积→保持压力稳定后开始淀积→关闭所有工艺气体,重新抽真空→回冲N2到常压→出片。

冷壁平行板PECVD如图4.16所示。

图4.16 冷壁平行板PECVD

典型等离子增强化学气相沉积系统不像前面所提的常压或低压化学气相沉积系统,必须靠唯一的热能来维持反应的继续进行,它是靠射频感应所产生的灼热放电,并且把能量转换到反应气体上,所以它的基板温度比常压或低压化学气相沉积法低许多,低温沉积是等离子增强化学气相沉积法最主要的优点。事实上,等离子增强化学气相沉积法提供了一种在基板上镀膜的方法,而且没有在镀膜时出现热稳定性的问题。此外,等离子增强化学气相沉积法能增进镀膜的速率,比只使用靠热反应来得更快,而且能提供唯一成分及特性的薄膜,但是生产量、生产力的限制(特別是大尺寸的晶片),因松散的黏附性所造成的微尘物污染仍旧是最大的问题。

接下来将探讨等离子增强化学气相沉积的方法,首先借由引入射频场(RF-field)进入低压的气体中,在放电区域产生自由电子,于是形成了离子。电子即从电场中获得能量,当带有能量的电子和气体分子碰撞后,反应的气体如硅烷(SiH4)、笑气(N2O)、氧气、氮气等就会分解,并且离子化,这些充满能量的反应物就都会在基板表面吸附。这些激发的原子团,在被吸收后有很高的黏附系数,而且也很容易在基板表面上迁移,这两个因素使得镀出来的薄膜有很好的一致性。这些被吸附到基板表面的激发原子团受到离子、电子的撞击以重新排列,并且和其他被吸附的反应物反应,形成新的键结,于是薄膜因而生成。原子的重新排列包括了被吸附原子扩散到稳定的位置上去并且把反应后的副产物(废物)脱离基板表面,而这脱离的速率由基板的温度决定,基板的温度越高,所镀上的薄膜拥有越少的副产物(这些副产物在薄膜里面将造成缺陷)。

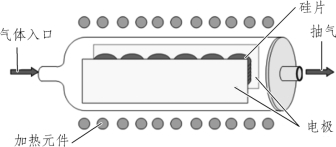

热壁平行板PECVD如图4.17所示。

图4.17 热壁平行板PECVD

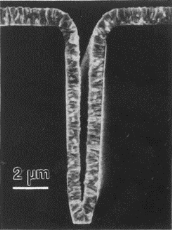

另外要注意的是要避免同质的气相成核反应(Homogeneous Gas-phase Nucleation),因为这将造成微尘物的污染。CVD淀积钨电镜照片如图4.18所示。

图4.18 CVD淀积钨电镜照片

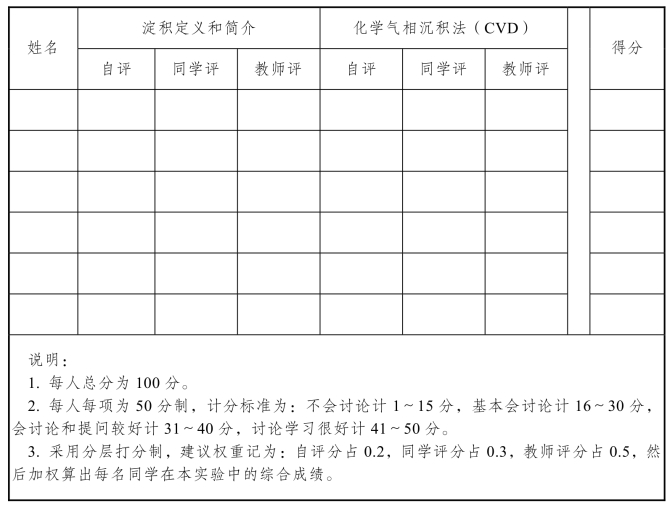

任务二学习成果评价

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。