1.Wafer Fabrication

Wafer Fabrication(晶圆制造):本工序的主要工作是在晶圆上制作电路及电子元件(如晶体管、电容、逻辑开关等),其处理程序通常与产品种类和所使用的技术有关,但一般基本步骤是先将晶圆适当清洗,再在其表面进行氧化及化学气相沉积,然后进行涂膜、曝光、显影、蚀刻、离子植入、金属溅镀等反复步骤,最终在晶圆上完成数层电路及元件加工与制作。

2.IDM

IDM(Integrated Device Manufacturer)是集成商模式,集设计、制造、封装测试为一体。IDM指的是垂直整合制造商,即涵盖了集成电路设计、晶圆制造、封装和测试所有环节的模式。该模式对技术和资金实力均具有很高的要求,为少数国际大型企业所采纳,如英特尔、三星、德州仪器等。

3.Foundry

Foundry指的是晶圆委外加工厂商,其自身不设计集成电路,而是受集成电路设计企业的委托,为其提供晶圆制造服务。由于晶圆生产线的投入很大,且工艺水平要求较高,这类企业一般具有较强的资金实力和工艺水平。Foundry模式的集成电路制造具有规模经济效益,适合大规模生产,同时集成电路制造具有重资产、重技术的特点,产线建设成本高、沉没成本高。采用此类模式的企业包括台积电、X-FAB、中芯国际等。

4.Fabless

Fabless指的是无晶圆厂的集成电路设计企业,其主要从事集成电路的设计和销售,而将晶圆制造、封装及测试环节通过委外方式进行处理。该模式下,集成电路设计企业可以专注于集成电路的研发,而不必投资大量资金建设晶圆生产线、封装测试工厂等。目前,全球绝大多数集成电路企业均为Fabless模式,包括美国高通等。

芯片设计已成为集成电路产业的上游,起到“龙头”作用,Fabless经营模式主要一般为:组织研发人员进行芯片设计,形成设计版图;将版图交给晶圆委外加工厂商,委托其加工生产晶圆片;将加工好的晶圆片交给封装测试企业,委托其进行晶圆的切割、封装和测试,得到芯片成品;将芯片成品直接或通过经销商销售给方案商、模组厂或整机厂等下游客户。

与其他类型的企业相比,Fabless的运营模式有利于提升新技术和新产品的开发速度,确保企业始终站在行业技术前沿,保持并扩大自身技术优势。由于这种模式下的初始投资规模较小,对企业的资金负担不大,后续也不需要过高的管理成本,因此这种模式也得到了许多轻资产的IC设计企业的青睐。芯片本身是一种高精密度的器件,这种模式下虽然可以降低成本,但同样也要承受制造工艺质量、市场问题等风险。

5.Wafer

Wafer(晶圆),是指硅半导体集成电路制作所用的硅晶片,由于其形状为圆形,故称为晶圆[1]。

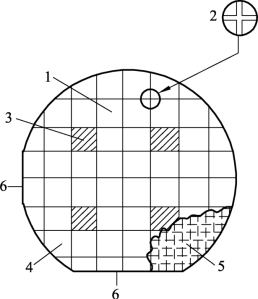

其原始材料是硅。高纯度的多晶硅溶解后掺入硅晶体晶种,然后慢慢拉出,形成圆柱形的单晶硅,硅晶棒在经过研磨、抛光、切片后,形成硅晶圆片,也就是晶圆。业界经常说的6 inch、8 inch、12 inch指的就是晶圆生产线的尺寸。Wafer一般由晶圆厂,如台积电、三星等Fab生产制造。晶圆结构如图1.11所示,下面具体进行讲解。数字1为芯片(chip)、die器件(device)、电路(circuit)、微芯片(microchip)或条码(bar):所有这些名词指的是在晶圆表面占大部分面积的微芯片图形。Die:一片Wafer上的一小块晶片晶圆体。由于Die 尺寸(size)的不同,一片Wafer所能容纳的Die数量不同。Die一般由封装厂对Wafer进行切割而得。Chip:封装厂将Die加个外壳封装成可以焊在电路板上的芯片。

图1.11 晶圆结构

数字2为划片线(scribe line),划锯线(saw line)或街区(street avenue):这些区域是在晶圆上用来分隔不同芯片之间的间隔区。划片线通常是空白的,但有些公司在间隔区内放置对准标记,或测试的结构。

数字3为工程试验芯片(engineering die)和测试芯片(test die):这些芯片与正式器件芯片或电路芯片不同。它包含特殊的器件和电路模块用于对晶圆生产工艺的电性测试。

数字4为边缘芯片(edge die):在晶圆的边缘上的一些掩模残缺不全的芯片而产生的面积损耗。由于单个芯片尺寸增大而造成的更多边缘浪费会由采用更大直径晶圆所弥补。推动半导体工业向更大直径晶圆发展的动力之一就是为了减少边缘芯片所占的面积。

数字5为晶圆的晶面(wafer crystal plane):图中的剖面标示了器件下面的晶格构造。此图中显示的器件边缘与晶格构造的方向是确定的。

数字6为晶圆定位边(Wafer Flats)/凹槽(Notches):例如图示的晶圆有主定位边(Major Flat)和副定位边(Minor Flat)。300 mm和450 mm直径的晶圆都是用凹槽作为晶格导向的标识。这些定位边和凹槽在一些晶圆生产工艺中还辅助晶圆的套准。

6.CP

CP(Chip Probing,晶圆测试)的测试对象是Wafer,目的是筛选出坏的Die并且喷墨标识,使其在封装环节前被淘汰掉,能减小封装和测试的成本。基本原理是下探针加信号激励给Die,然后测试功能。CP一般在晶圆厂进行。

7.FT

FT(Final Test,最终测试)的测试对象是Chip,目的是筛选符合设计要求的芯片,然后将芯片卖给客户。FT一般在封装厂进行。

8.MPW

MPW(Multi Project Wafer,多项目晶圆),就是将多个使用相同工艺的集成电路设计放在同一晶圆片上流片,制造完成后,每个设计可以得到数十片芯片样品,这对于原型(Prototype)设计阶段的实验、测试已经足够了。MPW有点类似于拼团,晶圆厂会给出一个特定时间,让芯片公司一起流片(Tape Out),这个过程也称为Shuttle(穿梭往返)。该次制造费用由所有参加MPW项目的公司按照Die size分摊,这可以极大地降低产品开发风险,但是要赶时间,错过了只能等下次了。

9.国家、行业标准界定的术语和定义

以下术语和定义适用于“1+X”集成电路开发及应用标准:

(1)晶圆(Wafer):一个或多个电路或器件在其中制成的半导体材料或是在某种衬底上淀积的一种材料,一般是扁而圆的片子。

(2)单晶硅片(Mono Crystalline Silicon Chip):由单晶硅锭上切割下的,或经研磨、抛光等后续加工处理的圆盘状硅单晶薄片。

(3)单晶炉(Crystal Growing Furnace):以高温熔化方法由原材料制备或提纯单质或化合物半导体单晶锭的设备。

(4)切片机(Slicing Machine):将半导体单晶等脆硬棒材切割成适当厚度片材的设备。

(5)氧化(Oxidation):指将氧气加入硅晶圆后在晶圆表面形成二氧化硅的过程。

(6)扩散(Diffusion):只由浓度梯度所引起的粒子运动。

(7)淀积(Deposition):又称沉积,是指在晶圆wafer上淀积一层膜的工艺。

(8)光刻(Photoetching或photolithography):平面型晶体管和集成电路生产中的主要工艺,是对半导体晶片表面的掩蔽物(如二氧化硅)进行开孔,以便进行杂质的定域扩散的一种加工技术。

(9)掩膜版(Mask):又称掩膜,是经曝光显影形成在基片上,用以选择性地阻挡辐射线或化学、物理腐蚀媒质穿透的抗蚀剂屏蔽图层。

(10)蚀刻(Etch):用化学或物理方法有选择地从硅片表面去除不需要的材料的过程。

(11)离子注入(Ion Implantation):指将被加速的离子注入半导体晶体中,在该晶体中形成P型、N型或本征电导率区域。

(12)测试机(IC Tester):测量集成电路管芯或封装后的集成电路器件电器参数的设备。

(13)集成电路(Integrated Circuit):将全部或部分电路元件不可分割地连在一起,并形成电互连,以致就结构和 产品而言被视为不可分割的微电路。

(14)封装(Package):对一个或多个半导体芯片、膜元件或其他元器件的包封,它提供电连接及机械和环境的保护。(https://www.daowen.com)

(15)划片机(Scribing Machine):在制有完整集成电路芯片的半导体圆片表面按预定通道刻画出网状沟槽,以便将其分裂成单个管芯的设备。

(16)引线键合(Wire Bonding):将管芯上的焊点和管座基板上的焊点用适当的细金属丝进行低阻连接的工序。

(17)点胶头(Dispenser Needle):属于自动装片机的配件产品,是在引线框架的芯片座上点银浆的部件。

(18)塑料封装机(Plastic Packaging Machine):又称塑封机,是在一定温度下,用模压塑封树脂对键合后的管芯进行封装的设备。

(19)打标机(Marker):将器件的商标、型号等标志清晰打印在器件封壳表面的设备。

(20)分选机(IC Sorter):与集成电路测试仪连接进行常温或高、低温条件下的集成电路测试和分类的设备。

(21)原理图(Schematic Diagram):表示电路板上各器件之间连接原理的图表。

(22)印制电路板(PCB Printed Circuit Board):又称印刷电路板、印刷线路板,是重要的电子部件,是电子元器件的支撑体,是电子元器件电气连接的载体。

(23)PCB图(PCB Diagram):电路板的映射图纸,它详细描绘了电路板的走线,元件的位置等。

(24)物料清单(BOM,Bill of Material):描述产品零件、半成品和成品之间的关系。

(25)集成电路版图(IC Layout):简称版图,是指按照一定的集成电路工艺设计规则,将与电路中各种器件相对应的设计层次有序地排列、组合、叠加而形成的一套用于制作掩膜版的数据。

(26)光刻胶(Photoresists):一种有机化合物,是微电子技术中微细图形加工的关键材料之一。

(27)飞边(Burrs):又称溢边、披锋、毛刺等,大多发生在模具的分合位置上。

(28)测试夹具Test Fixture由众多金黄色的导电触片组成,因其表面镀金而且导电触片排列如手指状,所以又称为“金手指”。

(29)版图设计(Layout Design):指将前端设计产生的门级网表通过EDA(电子设计自动化)设计工具进行布局布线和进行物理验证并最终产生供制造用的GDSII(Geometry Data Standard Ⅱ,几何数据标准)数据。

任务四学习成果评价

本模块知识小结

本模块主要介绍了半导体产业发展的重要意义和半导体产业链,重点介绍了半导体发展方向的双轮驱动力及摩尔定律,最后介绍了半导体制造的专业术语。通过学习本模块内容,可使读者了解半导体产业链的上中下游产业,可掌握摩尔定律和特征尺寸概念,也可掌握IC的一些专业术语如IDM、Fabless和Foundry,这都可为读者理解与学习后续模块的内容奠定基础。

现场典型工作任务案例教学

模块一测评题

1.什么是半导体制造技术的特征尺寸?

2.半导体制造的摩尔定律是什么?

3.2018年中国进口集成电路总金额为3 120.6亿美元(20 584.1亿元),集成电路进口额第一次超过___亿美元,进口额不仅超过了原油这一战略物资,而且超过了农产品、铁矿、铜、铜矿、医药品的总和。通过上数据如何去理解半导体产业链对我国国民经济的意义?

4.如何理解中美的“芯片之战”就是国家之战、未来之战?

5.学好“现代集成电路制造工艺”课程的意义是什么?

6.解释下列术语:

(1)CD (2)Character window

(3)Chemical-mechanical polish(CMP)(4)Chemical vapor deposition(CVD)

(5)Chip (6)CIM

(7)Circuit design (8)Clean room

(9)Compensation doping (10)CMOS

(11)Computer-aided design(CAD) (12)Conductivity type

(13)Contact (14)Control chart

(15)nanometer(nm) (16)nanosecond(ns)

模块一学习总结报告

【注释】

[1]本书前三个模块把没有电路功能的晶圆叫裸晶圆Wafer,业界也叫作硅片,即本书前三个模块中裸晶圆与硅片同义,模块3后的晶圆指的是有电路功能的IC Wafer。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。