I2C模块有如下相关寄存器:

●I2C自身地址寄存器:I2COAR。

●I2C中断使能寄存器:I2CIER。

●I2C状态寄存器:I2CSTR。

●I2C时钟低时间分频器寄存器:I2CCLKL。

●I2C时钟高时间分频器寄存器:I2CCLKH。

●I2C数据计数寄存器:I2CCNT。

●I2C数据接收寄存器:I2CDRR。

●I2C数据从地址寄存器:I2CSAR。

●I2C数据发送寄存器:I2CDXR。

●I2C模式寄存器:I2CMDR。

●I2C中断源寄存器:I2CISRC。

●I2C扩展模式寄存器:I2CEMDR。

●I2C预定标器寄存器:I2CPSC。

●I2CFIFO发送寄存器:I2CFFTX。

●I2CFIFO接收寄存器:I2CFFRX。

●I2C接收移位寄存器:I2CRSR(CPU不能访问)。

●I2C发送移位寄存器:I2CXSR(CPU不能访问)。

下面详细介绍这些寄存器。

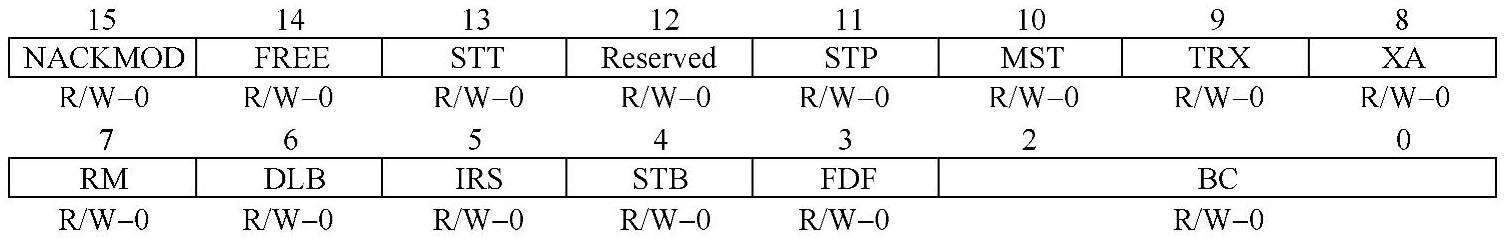

1.模式寄存器I2CMDR

寄存器I2CMDR(I2C Mode Register)是一个16位寄存器,包含I2C模块的所有控制位。格式如下。

位15,NACKMOD:NACK模式位。该位只有当I2C模块为接收状态时才有效。

●0:从接收模式。在总线的每个ACK周期,I2C模块都要发送一个ACK位到发送器。

如果设置了NACKMOD位,I2C模块仅发送一个NACK位。

主控接收模式:在总线的每个ACK周期,I2C模块都要发送一个ACK位到发送器,直到内部的数据计数器计数到0为止。数据计数器计数为0时,I2C模块发送一个NACK位到发送器。如果设置了NACKMOD位,I2C模块会早些发送一个NACK位。

●1:从动接收/主控接收模式。I2C模块在总线的下一个应答周期发送一个NACK位到发送器。一旦发送了NACK位,就清除NACKMOD位。

注意:为了在总线的下一个周期发出一个NACK位,在最后一个数据位的上升沿之前,用户必须设置NACKMOD位。

位14,FREE:仿真调试控制位。当仿真调试器遇到断点时,该位控制I2C模块在仿真调试时所做的动作。

●0:主模式。当中断发生时,如果SCL为低,I2C模块立即停止并且保持SCL为低(不论I2C模块为接收还是发送)。如果SCL为高电平,I2C模块处于等待状态直到SCL变为低,然后停止。

从模式:当前的发送或者接收任务完成时,断点可以强制停止I2C模块。

●1:自由运行。当一个中断发生时,它仍然继续运行。

位13,STT:启动(START)条件位,仅仅用于I2C模块为主模式。当I2C模块启动与停止数据传送时,会检测RM、STT及STP位。STT位与STP位可用于终止重复模式,当IRS=0时,不能写STT位。

●0:在主控模式时,启动(START)条件产生后,STT自动清除。

●1:在主控模式时,置位STT为1。引起I2C模块在总线上产生一个启动(START)条件。

位12,保留位。

位11,STP:停止(STOP)条件位,仅仅用于I2C模块为主控模式。在主模式下,当I2C模块启动与停止数据传送时,会检测RM、STT及STP位。STT位与STP位可用于终止重复模式,当IRS=0时,不能写STP位。

●0:停止(STOP)条件产生后,STP自动清除。

●1:当内部的数据计数器计数到0,DSP产生一个停止(STOP)条件时,STP位置为l。

位10,MST:主模式位。不论I2C模块是处于主控模式还是从动模式,都会检测MST位。当I2C模块产生一个停止(STOP)条件时,MST位自动从1变到0。

●0:从模式。I2C模块工作于从模式,从主器件接收串行时钟脉冲。

●1:主模式。I2C模块工作于主模式,在SDL引脚上产生串行时钟脉冲。

位9,TRX:发送模式位。TRX选择I2C模块是处于发送模式还是接收模式。

●0:接收模式。I2C模块为一个接收器,从SDA引脚接收数据。

●1:发送模式。I2C模块为一个发送器,从SDA引脚发送数据。

位8,XA:扩展地址使能位。

●0:7位地址格式。I2C模块发送7位从地址(从地址寄存器(I2CSAR)中位6~0),它自身有7位从地址(自身地址寄存器(I2COAR)中位6~0)。

●1:10位地址格式(扩展地址格式)。I2C模式发送10位从地址(从地址寄存器I2CSAR中位9~0),它本身有10位从地址(自身地址寄存器I2COAR中位9~0)。

位7,RM:重复模式位(只适用于I2C模块为主发送模式)。当I2C模块启动和停止数据传输时将检测RM、STT、STP位。

●0:非重复模式。数据计数寄存器(I2CCNT)的值确定还有多少字节要通过I2C模块发送或接收。

●1:重复模式。每当数据发送寄存器(I2CDXR)写入数据就启动一次字节发送,直到用户设置STP位为1(或在FIFO模式时,发送FIFO寄存器为空),忽略数据计数寄存器(I2CCNT)的值。当数据发送寄存器(I2CDXR)或FIFO中更多的数据准备好时,使用ARDY位和中断,直到所有数据已经传送或者CPU写了停止(STP)位为止。

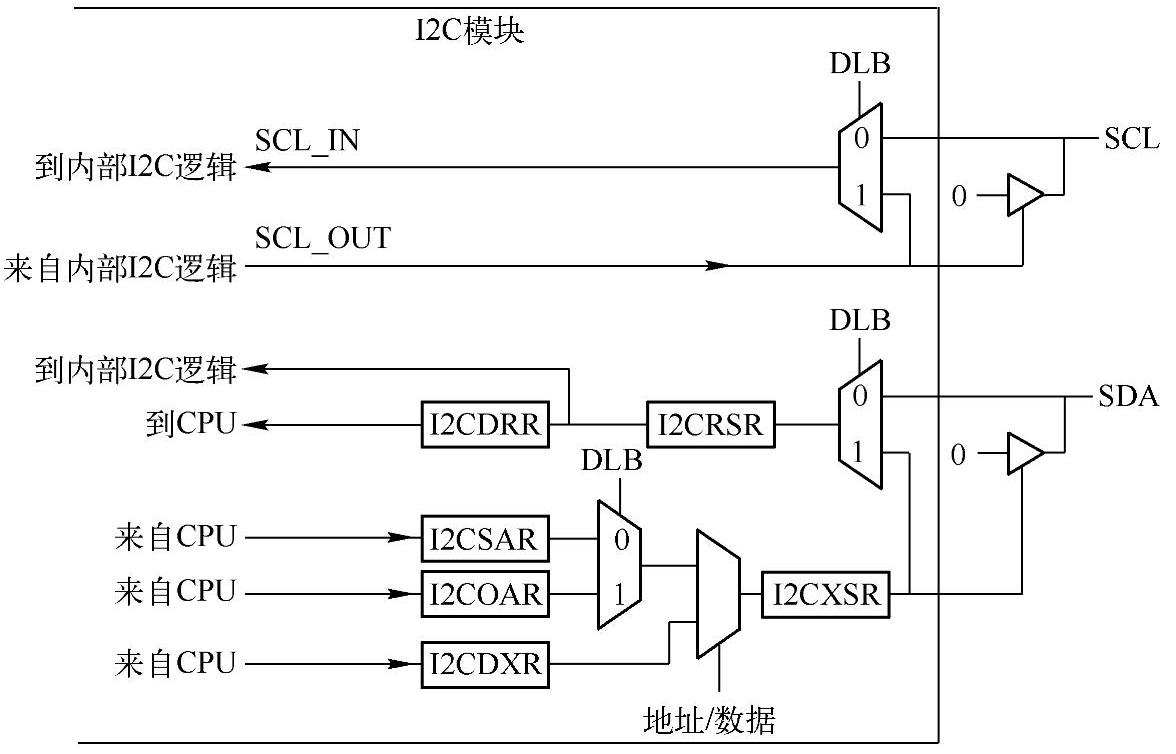

位6,DLB:数字回环模式位。

●0:禁止数字回环模式。

●1:使能数字回环模式。为了正确使用这个模式,MST位必须设置为1。

在数字回环模式中,数据发送寄存器(I2CDXR)发送出去的数据在N个时钟周期后通过一个内部路径返回到数据接收寄存器(I2CDRR)接收。

N=(I2C模块输入时钟频率/模块时钟频率)×8

发送时钟频率与接收时钟频率相等。在SDA引脚上发送的地址是自身地址寄存器(I2COAR)中的地址。数字回环模式位(DLB)的作用如图13-14所示。注意:数字回环模式不支持自由数据格式(FDF=1)。

位5,IRS:I2C模块复位位。

●0:复位/禁止I2C模块。当该位清0时,设置状态寄存器(I2CSTR)状态位为默认值。

图13-14 DLB模式位作用框图

●1:使能I2C模块。如果I2C外部设备悬挂,可以通过该位释放I2C总线。

位4,STB:启动(START)字节模式位。只有I2C模块为主控模式时,该位有效。从动需要较长的时间来检测一个启动(START)条件,而启动字节可用于帮助从动来检测启动(START)条件。当I2C模块为从模式时,不论STB的值是什么,它将忽略主器件中的启动(START)字节。

●0:I2C模块不处于启动字节模式。

●1:I2C模块为启动字节模式。当用户设置启动(START)条件位(STT)时,I2C模块开始传送比一个启动(START)条件更多的信息。

一个启动(START)条件。

一个启动(START)字节(00000001b)。

一个虚读应答时钟脉冲。

一个重复的启动(START)条件。

然而通常I2C模块发送从地址寄存器(12CSAR)中的从地址。

位3,FDF:自由数据格式模式位。

●0:禁止自由数据格式模式。通过XA位选择使用7位/10位地址格式。

●1:使能自由数据格式模式。使用自由数据格式(没有地址)。

在数字回环模式(DLB=1)中小支持自由数据格式。

位2~0,BC:计数位,BC定义下一个字节的位数。BC选定的位数必须与其他驱动器数据位数相匹配。当BC=000b时,数据字节为8位。BC不影响地址字节(总是8位)。

●000:每字节8位。

●001:每字节1位。

●010:每字节2位。

●011:每字节3位。

●100:每字节4位。

●101:每字节5位。

●110:每字节6位。

●111:每字节7位。

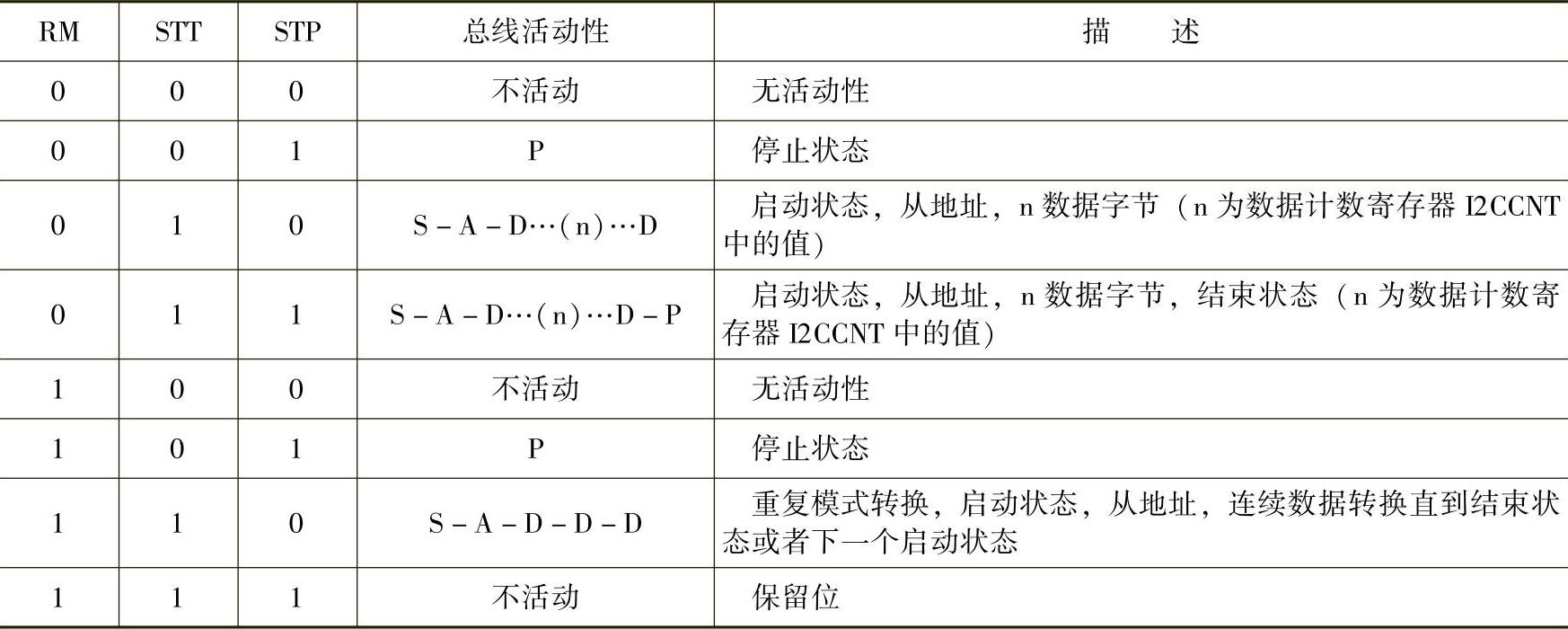

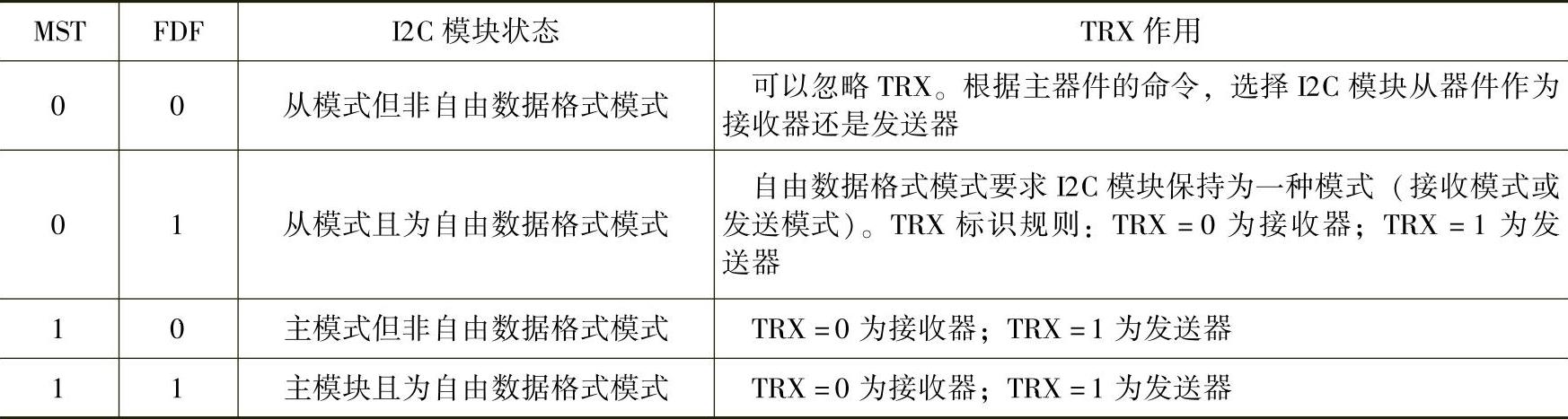

通过RM、STT和STP(I2CMDR)配置主控接收与发送总线活动情况见表13-4。修改MST和FDF位对TRX位的影响见表13-5。

表13-4 通过RM、STT和STP(I2CMDR)配置主控接收与发送总线活动情况

注:S为启动状态;A为地址;D为数据字节;P为停止状态。

表13-5 MST、FDF位对TRx位的影响

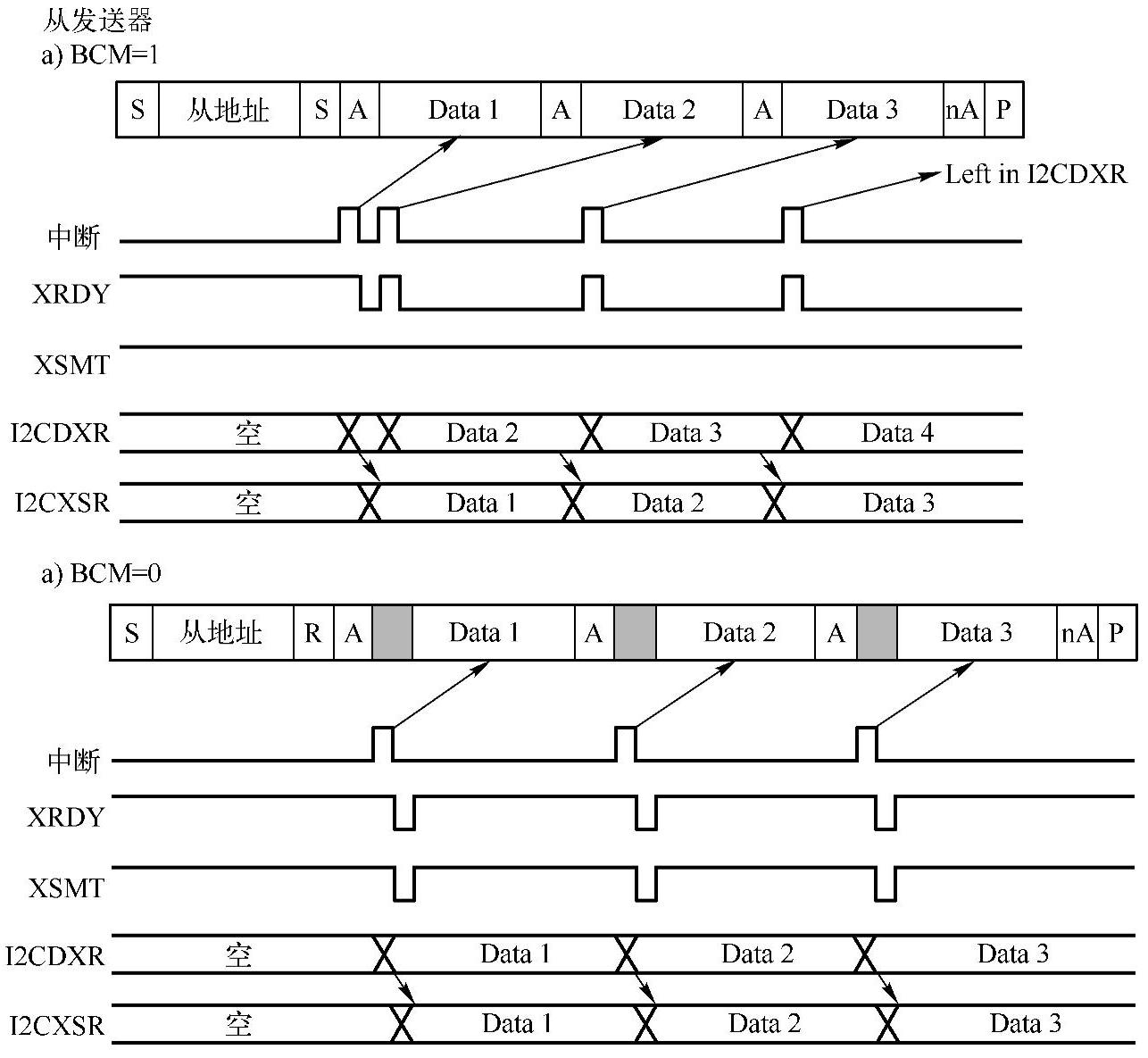

2.I2C模块扩展模式寄存器I2CEMDR

寄存器I2CEMDR(I2C Extended Mode Register)的位15~l位保留位。

位0,BCM:向后兼容模式位。在从传送模式下,该位影响传送状态位[状态寄存器(I2CSTR)的XRDY和XSMT位]的时序,如图13-15所示。

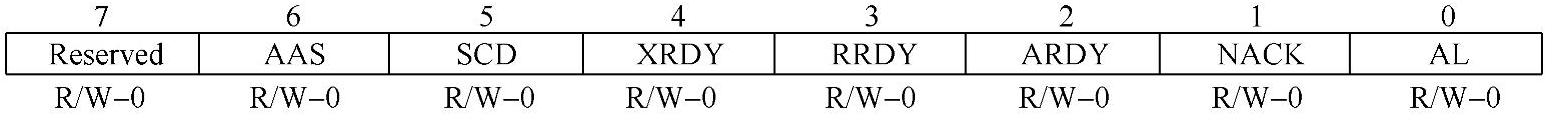

3.I2C模块中断使能寄存器I2CIER

寄存器I2CIER(I2C Interrupt Enable Register)用来使能或禁止I2C中断请求,其各位功能如下。

位15~7,保留位。

位6,AAS:从地址中断使能位。

●0:禁止中断请求。

图13-15 从传送模式下BCM位的影响

●1:使能中断请求。

位5,SCD:停止(STOP)条件检测中断使能位。

●0:禁止中断请求。

●1:使能中断请求。

位4,XRDY:发送数据就绪中断使能位,该位在FIFO模式不能设置。

●0:禁止中断请求。

●1:使能中断请求。

位3,RRDY:接收数据就绪中断使能位,该位在FIFO模式不能设置。

●0:禁止中断请求。

●1:使能中断请求。

位2,ARDY:寄存器就绪中断使能位。

●0:禁止中断请求。

●1:使能中断请求。

位1,NACK:不应答中断使能位。

●0:禁止中断请求。

●1:使能中断请求。

位0,AL:丢失仲裁中断使能位。

●0:禁止中断请求。

●1:使能中断请求。

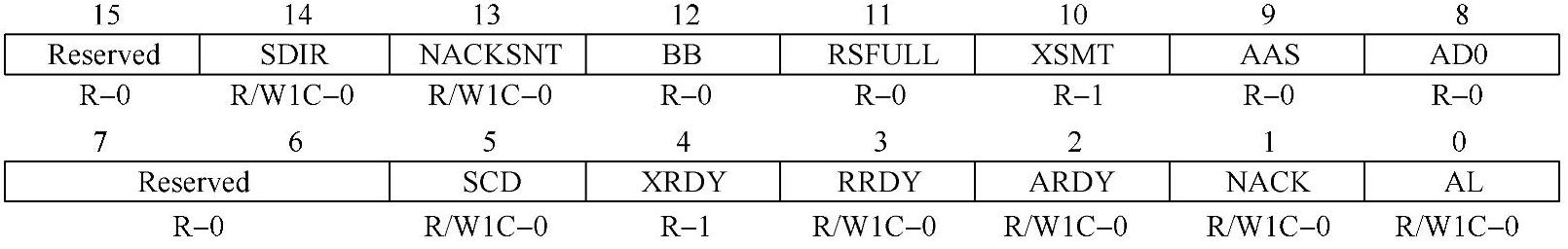

4.I2C模块状态寄存器I2CSTR

寄存器I2CSTR(I2C Status Register)是一个16位寄存器,用于判定已发生的中断,并且读取状态信息。该寄存器的各位及其功能如下。

位15,保留位。

位14,SDIR:从动方向位。

●0:I2C模块作为从发送器不分配地址。以下事件之一都能将SDIR清零:

手动写入1清零。

数字回环模式使能。

I2C总线上出现启动(START)或者停止(STOP)条件。

●1:I2C总线作为从发送器分配了地址。

位13,NACKSNT:NACK发送位,当I2C模式处于接收模式时使用该位。当使用不应答(NACK)模式时,NACKSNT受影响。

●0:没有发送NACK位。下列任何事件之一清零NACKSNT位:

手动写入1清零。

复位I2C模块(向IRS写入0或者器件复位)。

●1:发送NACK位。在I2C总线上的应答周期内,发送了不应答位。

位12,BB:总线忙位。BB位给另外的数据传送器指明I2C总线是处于忙或空闲状态。写入1清0该位。

●0:总线空闲。下列任何事件之一都能清零BB位。

I2C模式接收或者发送一个停止位(总线空闲)。

手动清零BB位,写入1清零。

复位I2C模块。

●1:总线忙。在I2C模式时,总线上已经发送或者接收一个启动位。

位11,RSFULL:接收转换寄存器溢出位。RSFULL表示接收时的溢出情况。当新的数据转移到接收转换寄存器(I2CRSR),且原来的数据没有从数据接收寄存器(I2CDRR)中读取时,就会发生溢出情况。

●0:没有溢出发生。下列任何事件之一都能清零RSFULL位。

CPU读数据接收寄存器(I2CDRR)寄存器。仿真器读数据接收寄存器(I2CDRR)寄存器,不会影响此位。

复位I2C模块。

●1:发生了溢出。

位10,XSMT:传送移位寄存器空。XSMT=0表示传送已发生下溢。若传送移位寄存器(I2CXSR)为空,而且最后一个从数据发送寄存器(I2CDXR)到I2CXSR的传送之后没有装载数据发送寄存器(I2CDXR),则发生下溢。直到数据发送寄存器(I2CDXR)中装载新数据时,下一个数据发送寄存器(I2CDXR)到I2CXSR的传送才发生。如果没有及时传送新数据,那么原来的数据可能在SDA引脚再次发送。

●0:检测到下溢(空)。

●1:未检测到下溢(不空)。通过下列事件之一能置位XSMT位。

写数据到数据发送寄存器(I2CDXR)。

复位I2C模块。

位9,ASS:从地址位。

●0:在7位地址格式时,当接收到一个NACK、一个停止(STOP)条件或者一个启动(START)条件时,将清零ASS位。在10位地址格式中,当接收到一个NACK、一个停止(STOP)条件或者一个与I2C模块外设本身从地址不同的从地址时,将清零ASS位。

●1:I2C模式有验证过的自己的从地址并且全为0(产生一个呼叫信号)时,置位ASS位。在自由模式下(模式寄存器I2CMDR中的FDF=1),如果接收到第一字节,也置位ASS位。

位8,ADO:地址的0位。

●0:启动(START)条件或者停止(STOP)条件清零ADO。

●1:检测到一个全为0的地址(常规的呼叫)。

位7~6,保留位。

位5,SCD:停止(STOP)条件检测位。当I2C模块发送或接收到一个停止(STOP)条件时,置位SCD位。

●0:没有检测到停止(STOP)条件,SCD位为0。(www.daowen.com)

下列事件之一将清零SCD位:

当I2CSRC寄存器中包含110b(检测到停止(STOP)条件)值时,CPU读I2CSRC寄存器。仿真器读I2CSRC寄存器,不影响此位。

通过写入1清零SCD位。

复位I2C模块。

●1:在I2C总线上检测到一个停止(STOP)条件。

位4,XRDY:数据发送准备好中断标志位。不用FIFO模式中时,由于原来的数据已经从数据发送寄存器I2CDXR中复制到发送转换寄存器I2CXSR中,XRDY表明数据发送寄存器I2CDXR已经准备好接收新数据。CPU能够查询XRDY或使用XRDY中断请求。在FIFO模式中,可以使用TXFFINT来代替。

●0:数据发送寄存器(I2CDXR)未准备好,当数据写入数据发送寄存器(I2CDXR)时,清零XRDY位。

●1:数据发送寄存器(I2CDXR)准备好,数据已经从数据发送寄存器复制到I2CXSR。

当复位I2C模块时,强制置位XRDY位。

位3,RRDY:数据接收准备好中断标忐位。不用FIFO模式中时,闪为数据已经从接收转换寄存器(I2CRSR)复制到数据接收寄存器(I2CDRR),所以RRDY表明数据接收寄存器(I2CDRR)已经准备好接收数据。CPU能够查询RRDY或使用RRDY中断请求。在FIFO模式中,可以使用RXFFINT来代替。

●0:数据接收寄存器(I2CDRR)未准备好。下列事件之一将清零RRDY位:

CPU读数据接收寄存器(I2CDRR)。仿真器读数据接收寄存器(I2CDRR)将不影响此位。

通过写入1清零RRDY位。

复位I2C模块。

●1:数据接收寄存器(I2CDRR)准备好。数据已经从12CRSR复制到数据接收寄存器(12CDRR)。

位2,ARDY:寄存器存取准备好中断标志位(仅当I2C模式为主控模式时才有效)。由于先前程序使用的地址、数据和命令值已经使用,ARDY位表明I2C模块寄存器已经准备好接受访问。CPU可以查询ARDY位或者使用ARDY中断请求。

●0:寄存器存取未准备好。通过下列事件之一将清零ARDY位:

I2C模块已经开始使用当前寄存器中的值。

一通过写入1清零ARDY位。

复位I2C模块。

●1:寄存器存取准备好。

在非重启模式中(在模式寄存器I2CMDR中的RM=0),如果模式寄存器(I2CMDR)中STP=0,数据计数器减到0,置位ARDY位;如果STP=1,则ARDY位不会受到影响。此时,当数据计数器减到0时,I2C模块产生停止(STOP)条件。

在重启模式中(在模式寄存器I2CMDR中的RM=1),ARDY位将在数据发送寄存器(I2CDXR)发送每个字节结束时置1。

位1,NACK:不应答中断标志位。当I2C模块作为一个发送器(无论是主还是从)时,将使用NACK位。NACK位表示I2C模块是否已经从接收器查询到一个应答值(ACK)或者一个不应答位(NACK)。CPU能查询NACK位或者使用NACK中断请求。

●0:ACK接收/NACK未接收。通过下列事件之一将清零NACK位:

接收器已经发送了ACK位。

通过写入1清零NACK位。

CPU读中断源寄存器(I2CISRC)并且该寄存器中包含NACK中断代码。仿真器读中断源寄存器(I2CISRC)将不影响此位。

复位I2C模块。

●1:接收到NACK位。硬件检测到不应答位(NACK)已经接收。

注意:即使一个或者更多的从动发送器应答,当I2C模块执行一个常规的呼叫发送时,NACK是1。

位0,AL:仲裁丢失中断标志位(仅仅当I2C位主发送模式时才有效)。AL表示I2C模块已丢失仲裁竞争给另一个主发送器。CPU能够查询AIL位或者使用AL中断请求。

●0:仲裁未丢失。下列事件之一将清零AL位:

写入1清零AL位。

CPU读中断源寄存器I2CISRC并且该寄存器中包含AL中断的代码。仿真器读中断源寄存器I2CISRC不影响此位。

复位I2C模块。

●1:仲裁丢失。下列事件之一将置位AL位:

I2C模块检测到几乎同时开始产生竞争的两个或多个发送器并丢失仲裁竞争。

当置位BB位(总线忙)时,I2C模块将试图启动一个发送数据的过程。

当AL变为1时,将清零模式寄存器(I2CMDR)的MST位和STP位,I2C模块转换成一个从接收器。

当I2C模块处于复位过程时,I2C模块外部设备不能检测到启动(START)条件或者停止(STOP)条件,例如,设置IRS位为0。因此,BB位将保持复位时的状态,直到I2C模块外部设备复位完成,BB位才会改变。例如,在I2C总线上检测到启动(START)条件或者停止(STOP)条件,IRS位将置1。

I2C模块发送数据前的初始化,必须按下面步骤进行:

①通过IRS位置1,使I2C模块跳出初始化。在第一个数据发送前,等待一定的周期来扫描总线状态。设置这个周期大于数据发送最大时间。在I2C模块完成复位后,等待一定的时间,用户能确定I2C总线上至少一个启动(START)条件或者停止(STOP)条件将发生,并且由BB位捕获。这个时间过后,BB位将正确反映I2C总线状态。

②在动作前检查BB位和核实是否BB=0(总线空闲)。

③开始数据发送。在发送期间不能复位I2C模块外部设备,此时BB位直接反映总线的实时状态。如果用户必须在发送期间复位I2C模块外部设备,重复步骤①~③,I2C模块外部设备将完成复位过程。

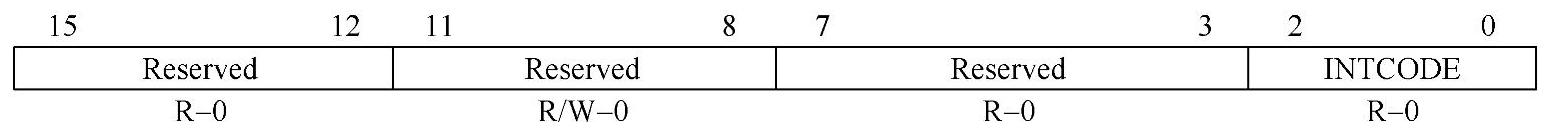

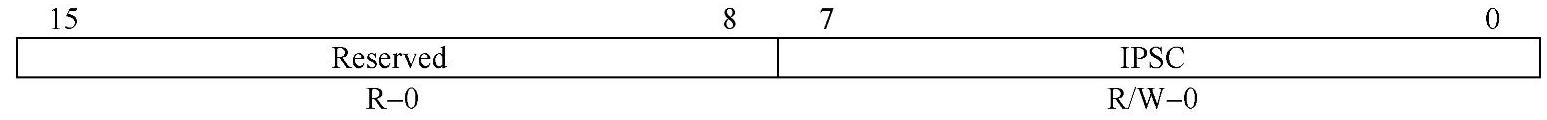

5.I2C模块中断源寄存器I2CISRC

寄存器I2CISRC(I2C Interrupt Source Register)是一个16位寄存器,表明产生中断的是哪一个事件。

位15~3,保留位。

位2~0,INTCODE:中断代码位。表示有一个I2C中断。

●000:无。

●001:仲裁丢失。

●010:检测到不应答条件。

●011:寄存器存取准备完成。

●100:接收数据准备完成。

●101:发送数据准备完成。

●110:检测到停止(STOP)条件。

●111:设置为从。

CPU读取时将清零这些位。如果另外的一个低优先级中断被悬挂或者使能,将装载相应的中断值。否则,将清零该值。

在仲裁丢失的情况下,检测到不应答条件或者停止(STOP)条件,CPU读取将清除状态寄存器(I2CSTR)中的相关中断标志位。

仿真器读取不影响状态寄存器(I2CSTR)中的状态位。

6.I2C模块预分频寄存器I2CPSC

I2C模块预分频寄存器I2CPSC(I2C Prescaler Register)是一个16位寄存器。它可以将I2C模块输入时钟分频成用户想得到的时钟频率。预分频值IPSC在I2C模块复位(IRS=0)时将初始化。预分频仅仅在IRS的值跳变到1之后才起作用。当IRS=1时,改变IPSC值是无效的。

位15~8,保留位。

位7~0,IPSC:I2C模块预分频值。IPSC确定CPU时钟的分频率:

模块时钟频率=I2C模块输入时钟频率/(IPSC+1)。

注意:IPSC必须在I2C模块复位时进行初始化。

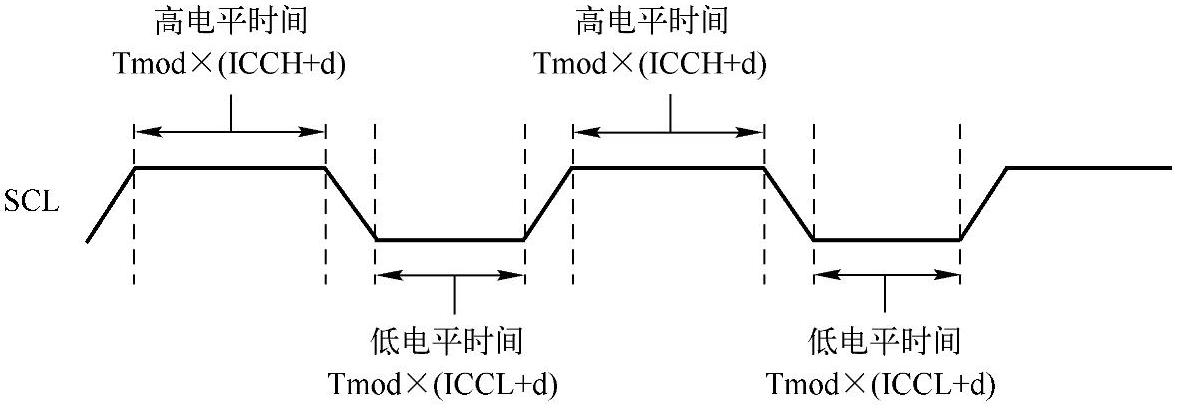

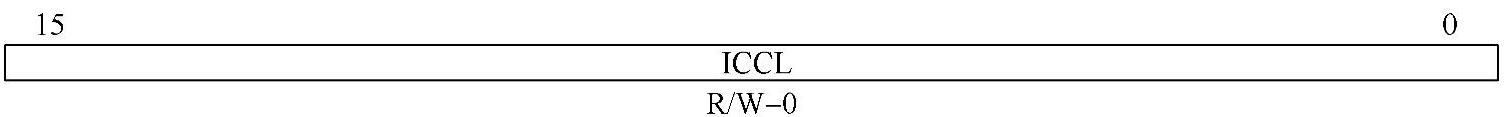

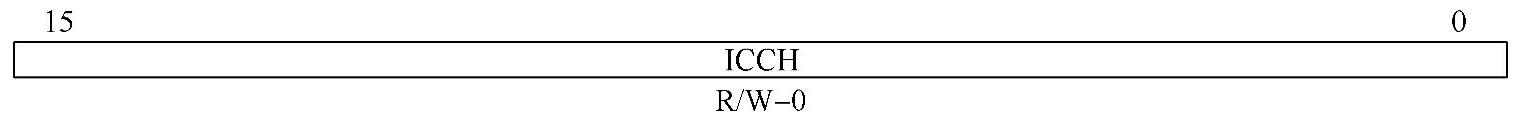

7.I2C模块时钟分频寄存器I2CCLKL和I2CCLKH

当I2C模块作为主控时,使用系统时钟分频得到在SCL引脚上的主控时钟信号,如图13-16所示,主控的时钟依赖这两个分频寄存器的值。

图13-16 时钟分频值(ICCL和ICCH)的作用

每一个主动时钟周期中ICCL(在时钟分频寄存器I2CCLKL中)确定低电平信号时间。每一个主动时钟周期中ICCH(在时钟分频寄存器I2CCLKH中)确定高电平信号时间。(1)I2C模块低电平时钟分频寄存器(I2CCLKL)

位15~0,ICCL:CLKL值。主控时钟的低电平持续时间,模块时钟周期与(ICCL+d)相乘。d为5、6或者7。注意:这些位必须设置为非零值,与I2C模块相适应。

(2)I2C模块高电平时钟分频寄存器(I2CCLKH)

位15~0,ICCH:CLKH值。主控时钟的高电平持续时间,模块时钟周期与(ICCH+d)相乘。d为5、6或者7。注意:这些位必须设置为非零值,与I2C模块相适应。

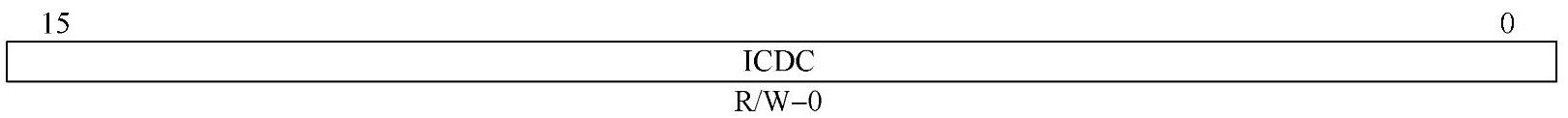

(3)主时钟周期方程

主时钟周期(Tmst)是模块时钟周期的倍数。

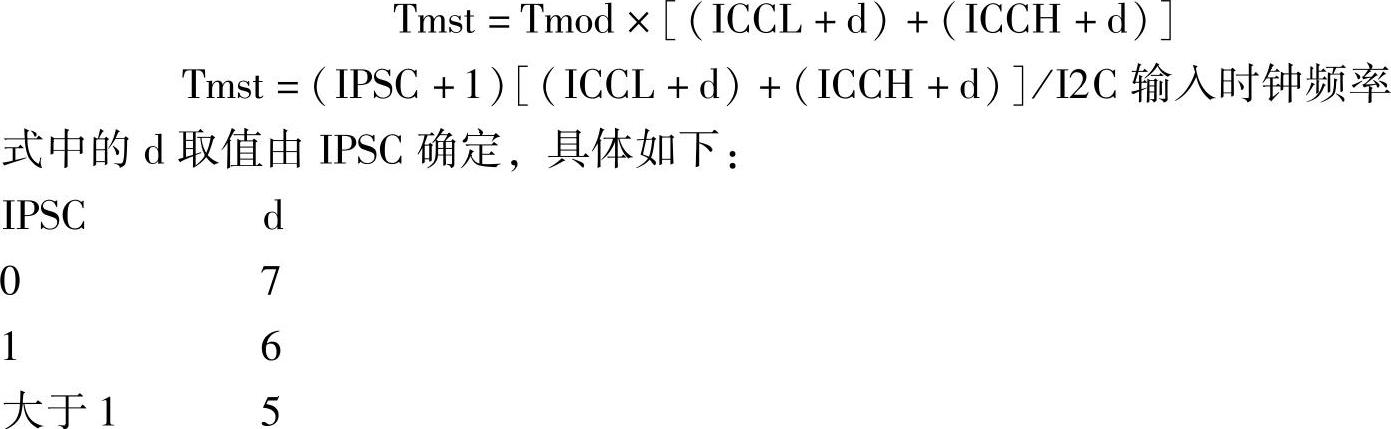

8.I2C模块从地址寄存器I2CSAR

寄存器I2CSAR (12C Slave Address Register)存储I2C模块主器件将要发送从器件的地址。它是一个16位的寄存器。从地址寄存器(12CSAR)的SAR位包含一个7位或者10位的从地址。当I2C模块不用自由模式(FDF =0)时,它用这个地址首先去与主控或从动进行通信。当地址为非0的时候,该地址是一个特定的从地址。当地址为0的时候,该地址是一个常规呼叫所有从器件地址。如果选择[模式寄存器(12CMDR)中的XA =0]7位地址格式,从地址寄存器(12CSAR)仅位0-6有效,位7-9需要写入0。

位15~10,保留位。

位9~0,SAR:从地址位。

●00h~7Fh:在7位地址格式(模式寄存器I2CMDR中的XA=0)时,当I2C模块存主发送模式时,位6~0给7位模式提供从地址。

●000h~3FFh:在10位地址格式(模式寄存器I2CMDR中的XA=1)时,当I2C模块存主发送模式时,位9~0给10位模式提供从地址。

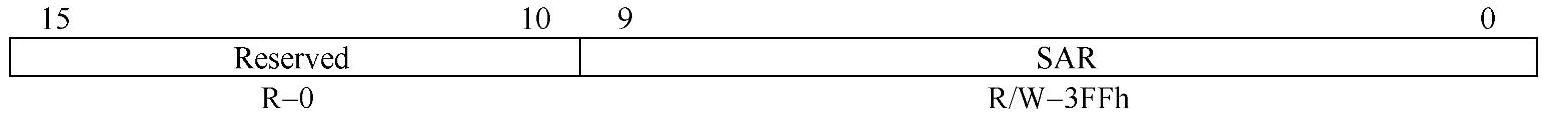

9.I2C模块自身地址寄存器I2COAR

寄存器I2COAR(I2C Own Address Register)是一个16位的寄存器。I2C模块用这个寄存器给自身一个特定的地址,这个地址有别于其他I2C总线上的从器件地址。如果选择7位地址格式(XA=0),仅仅位6~0有效,位7~9需要写入0。

位15~10,保留位。

位9~0,OAR:自身地址位。

●00h~7Fh:在7位地址格式中(模式寄存器I2CMDR中的XA=0),位6~0提供I2C模块的7位从地址,位9~7需要写入0。

●000h~3FFh:在10位地址格式中(模式寄存器I2CMDR中的XA=1),位9~0提供I2C模块的10位从地址。

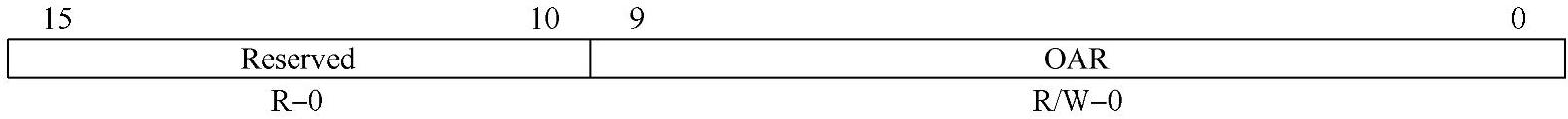

10.I2C模块数据计数寄存器I2CCNT

寄存器I2CCNT(I2 CData Count Register)是一个16位的寄存器,当I2C模块配置为主发送器或者主接收器时,数据计数寄存器(I2CCNT)表示发送的数据字节数。在重启模式(RM=1)时,不使用数据计数寄存器(I2CCNT)。

写入到数据计数寄存器(I2CCNT)中的值会复制到内部计数器中,每发送一个数据字节,内部计数器就减1(数据计数寄存器I2CCNT保持不变)。在主模式下,如果请求一个停止(STOP)条件(模式寄存器I2CMDR的位STP=1),那么I2C模块随着减计数完成,停止发送数据后将发送一个停止(STOP)条件。

位15~0,ICDC:数据字节计数值,表示发送或者接收数据的字节。当模式寄存器(I2CMDR)的RM位置1时,数据计数寄存器(12CCNT)的值是无效的。

●0000h:装入内部数据计数器的值为65 536。

●0001~FFFFh:装入内部数据计数器的值为1~65 535。

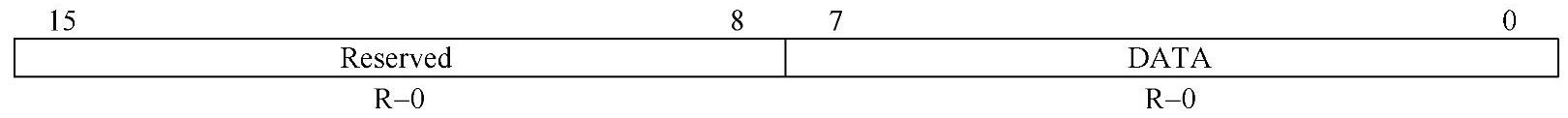

11.I2C模块数据接收寄存器I2CDRR

寄存器I2CDRR(I2C Data Receive Register)也是一个16位的寄存器,CPU通过该寄存器读取接收到的数据。I2C模块能接收一个1~8位的数据字节。该位的长度由模式寄存器(I2CMDR)中的BC位来确定。每次从SDA引脚上将一位数据传输到接收转换寄存器(I2CRSR)时,当一个完整的数据字节接收完成后,I2C模块将接收转换寄存器(I2CRSR)中的数据字节复制到数据接收寄存器(I2CDRR)中,CPU不能直接访问I2CRSR寄存器。

如果数据接收寄存器(I2CDRR)中的数据字节位数少于8位,那么字节将右对齐,并且其余位不确定。例如,如果BC=011(传送字节有3个数据位),那么,数据接收寄存器(I2CDRR)中接收数据的位3~7不确定。

位15~8,保留位。

位7~0,DATA:接收的数据。

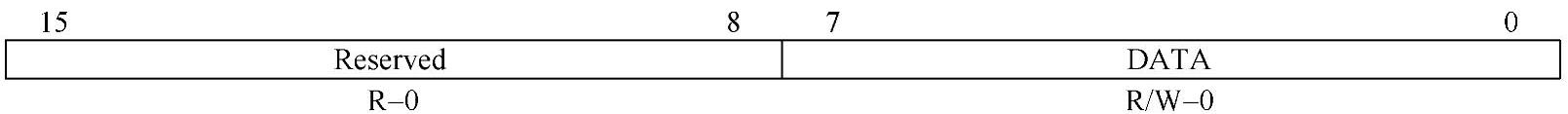

12.I2C模块数据发送寄存器I2CDXR

寄存器I2CDXR(I2C Data Transmit Register)中写入需要发送的数据字节,这16位寄存器接收1~8位的数据字节。在向数据发送寄存器(I2CDXR)写入数据之前,必须先向模式寄存器(I2CMDR)中BC位写入合适的值来确定数据发送寄存器(I2CDXR)中应该写入的数据字节的位数。当数据字节的位数少于8位时,写入数据发送寄存器(I2CDXR)中的数据必须是右对齐格式。

向数据发送寄存器(I2CDXR)写入数据字节后,I2C模块将数据字节复制到发送转换寄存器(I2CXSR)中。CPU不能直接访问I2CXSR。I2C模块自动从I2CXSR寄存器向SDA引脚一次一位地传送数据位。

位15~8,保留位。

位7~0,DATA:需要发送的数据。

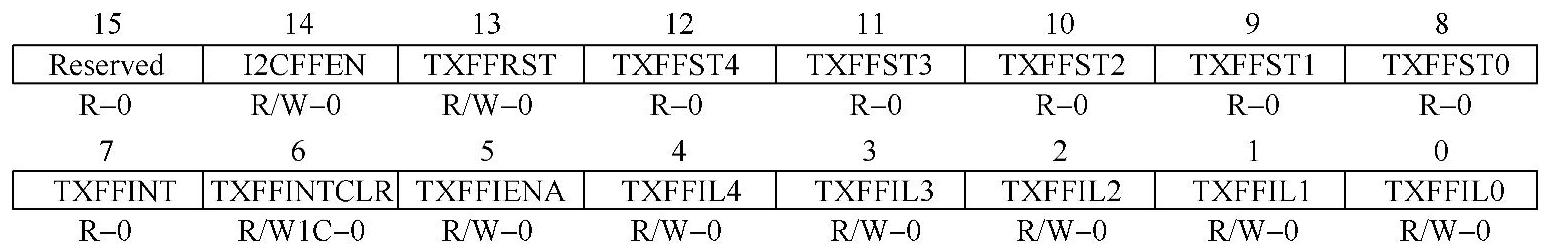

13.I2C模块发送FIFO寄存器I2CFFTX

寄存器I2CFFTX(I2C Transmit FIFO Register)是一个16位的寄存器,该寄存器包含I2C模块的FIFO模式使能位与外设操作模式的发送FIFO控制位和状态位。

位15,保留位。

位14,I2CFFEN:I2C模块FIFO模式使能位,该位必须正确设置为发送或者接收FIFO。

●0:禁止I2C模块FIFO模式。

●1:使能I2C模块FIFO模式。

位13,TXFFRST:I2C模块发送FIFO复位位。

●0:复位发送FIFO指针到0000,并保持发送FIFO寄存器为复位状态。

●1:使能发送FIFO操作。

位12~8,TXFFST4~0:发送FIFO的状态位。

●00xxx:发送FIFO包括xxx字节。

●00000:发送FIFO为空。

位7,TXFFINT:发送FIFO中断标志位。通过向TXFFINCLR位写入1来清零该位。如果TXFFIENA位置1,置位该位将产生一个中断。

●0:未产生发送FIFO中断。

●1:产生发送FIFO中断。

位6,TXFFINTCLR:发送FIFO中断标志清零位。

●0:写入0无效,读出为0。

●1:写入1清零TXFFINT标志。

位5,TXFFIENA:发送FIFO中断使能位。

●0:禁止发送FIFO中断,置位TXFFINT标志位不产生中断。

●1:使能发送FIFO中断,置位TXFFINT标志位产生中断。

位4~0,TXFFIL4~0:发送FIFO中断状态级。

通过该位域设置发送中断状态级。当TXFFST4~0位的值小于或等于该位域时,TXFFINT标志位置1,如果TXFFIENA位置1,将产生一个中断。

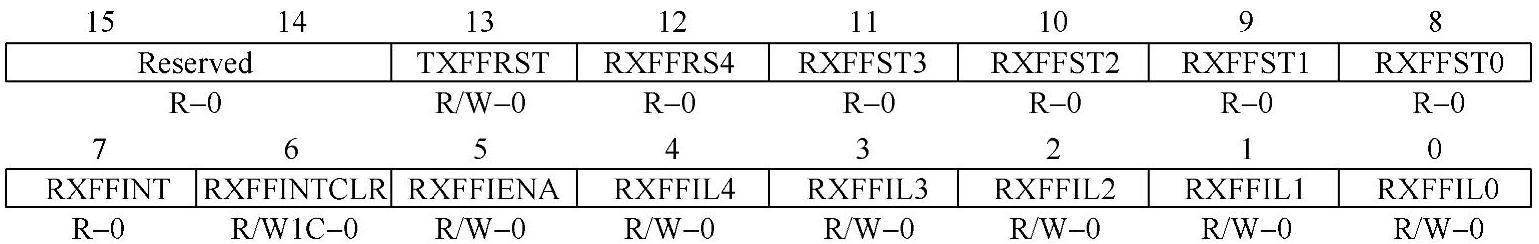

14.I2C模块接收FIFO寄存器I2CFFRX

寄存器I2CFFRX(I2C Receive FIFO Register)是一个16位寄存器,包含2C模块外设操作模式的接收FIFO控制位和状态位。

位15~14,保留位。

位13,RXFFST:I2C模块接收FIFO复位位。

●0:复位接收FIFO指针到0000,并保持接收FIFO寄存器为复位状态。

●1:使能接收FIFO操作。

位12~8,RXFFST4~0:接收FIFO内容的状态。

●00xxx:接收FIFO包含xxx字节。

●00000:接收FIFO位空。

位7,RXFFINT:接收FIFO中断标志位。通过写入1到RXFFINTCLR位清零该位。如果RXFFIENA位置1,那么置位该位将产生一个中断。

位6,RXFFINTCCLR:接收FIFO中断标志清零位。

●0:写入0无效,读出为0。

●1:写入1清除RXFFINT标志。

位5,RXFFIENA:接收FIFO中断使能位。

●0:禁止接收FIFO中断。置位RXFFINT标志位不产生中断。

●1:使能接收FIFO中断,置位RXFFINT标志位产生中断。

位4~0,RXFFIL4~0:接收FIFO中断优先级。

这些位域设置接收FIFO中断优先级。当RXFFST4~0位的值等于或小于该位域时,RXFFINT标志位置1。如果RXFFIENA位已经置1,将产生一个中断。

注意:该位域复位时为0,如果接收FIFO使能中断,且I2C模块完成复位过程,那么接收FIFO中断标志位将置1,将产生一个接收FIFO中断。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。