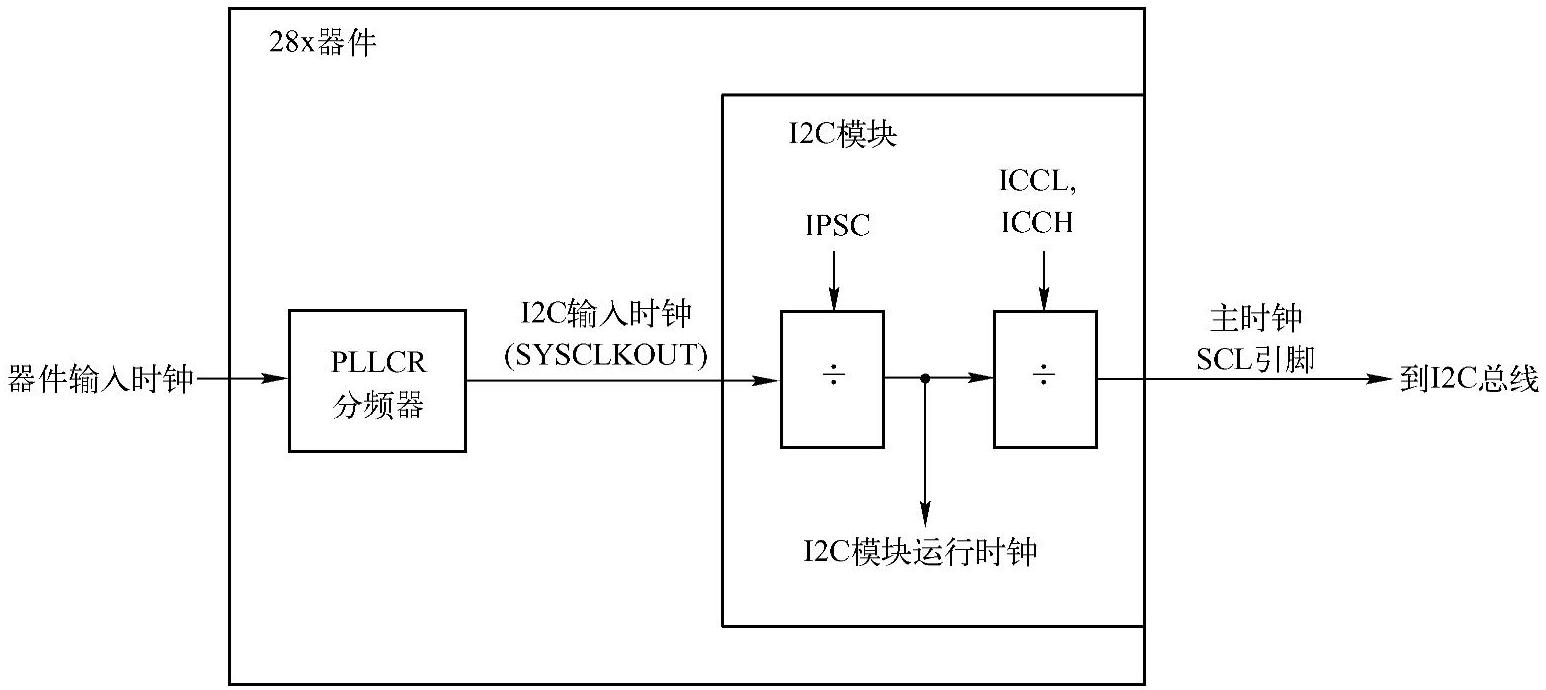

【摘要】:如图13-3所示,器件时钟发生器从外部时钟源接收信号,并根据程序设置的频率产生I2C输入时钟。I2C输入时钟与CPU时钟相等,并在I2C模块内两次分频产生模块时钟和主时钟。而只有当IRS由0变1时预定标产生的频率才起作用。时钟分频器采用I2CCLKL寄存器的ICCL值对模块时钟信号的低频段进行分频,采用I2CCLKH寄存器的ICCH值对模块时钟信号的高频段进行分频。图13-3 I2C模块时钟产生结构图

如图13-3所示,器件时钟发生器从外部时钟源接收信号,并根据程序设置的频率产生I2C输入时钟。I2C输入时钟与CPU时钟相等,并在I2C模块内两次分频产生模块时钟和主时钟。

模块时钟决定了I2C模块运行的频率。I2C模块内的一个可编程预定标器将I2C的输入时钟分频以产生模块时钟。为了确定分频值,可以初始化预定标寄存器的IPSC值。计算方法如下:

模块时钟频率=I2C输入时钟频率/(IPSC+1)

注意:为符合所有I2C模块的时间标准,模块时钟必须配置在7~12MHz范围内。

只有当I2C模块处于复位状态(I2CMDR的IRS位=0)时才能初始化预定标。而只有当IRS由0变1时预定标产生的频率才起作用。当IRS=l预定标频率无效时才能改变IPSC的值。(www.daowen.com)

当I2C模块配置为I2C总线的主模块时,SCL引脚输出时钟信号,该时钟控制I2C模块和从模块之间通信的时序。如图13-3所示,模块时钟经过再次分频作为主模块时钟。时钟分频器采用I2CCLKL寄存器的ICCL值对模块时钟信号的低频段进行分频,采用I2CCLKH寄存器的ICCH值对模块时钟信号的高频段进行分频。

图13-3 I2C模块时钟产生结构图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。

有关Piccolo系列DSP控制器原理与开发的文章