每个连接到I2C总线的器件都有一个唯一的识别地址。根据器件功能的不同,每个器件都可以实现发送或接收功能。当进行数据传输时,连接到I2C总线的器件都可以作为主器件或从器件。主器件初始化总线上的数据传输并产生时钟信号。在传输过程中,任何由该主器件寻址的器件都可以看作是从器件。I2C总线支持多个主器件模式,在这种模式下,能够控制I2C总线的一个或多个器件都可以连接到同一总线上。

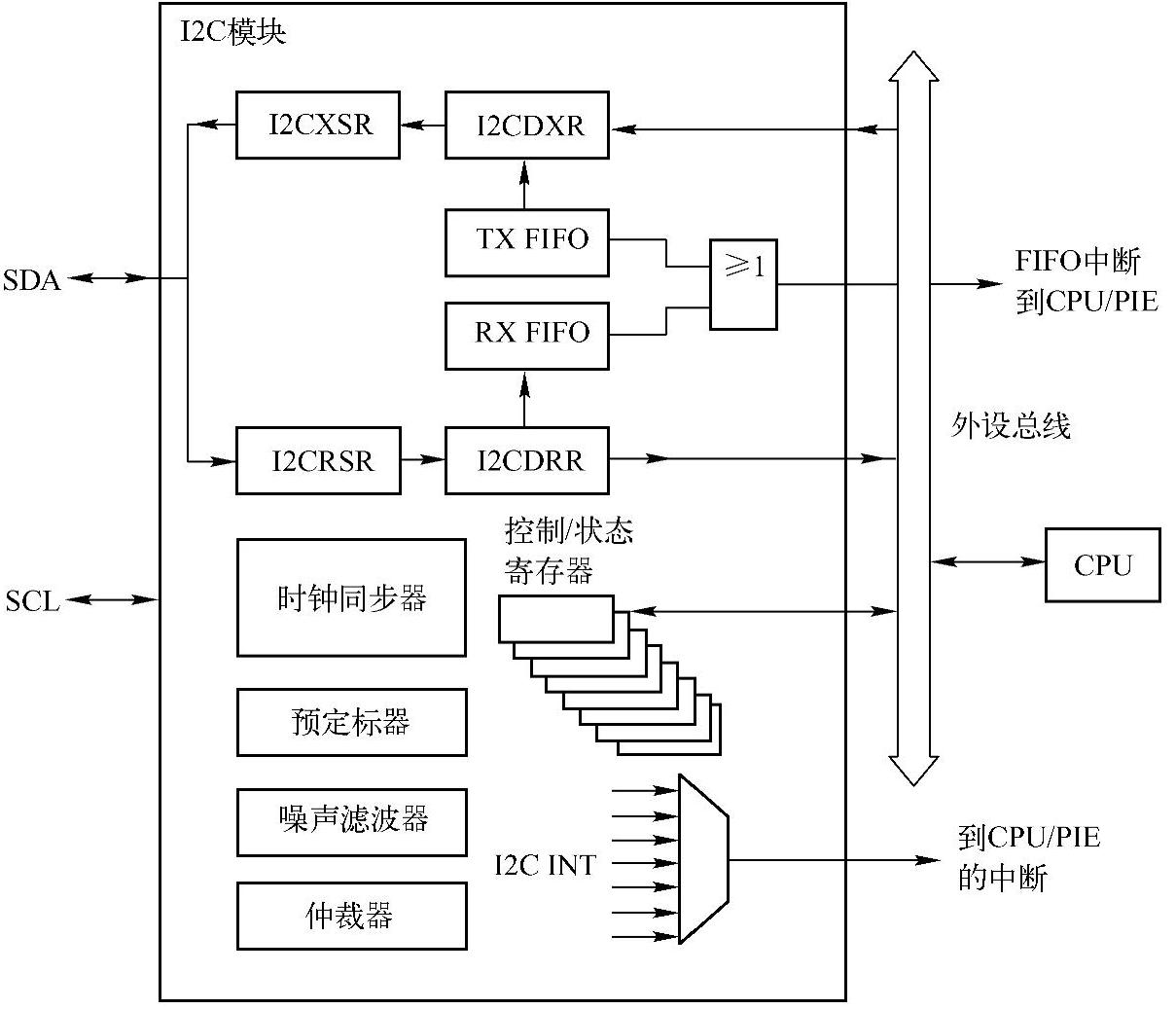

在实现数据传输时,I2C总线模块有一个数据引脚(SDA)和一个时钟引脚(SCL),如图13-2所示。这两个引脚在I2C总线的28x器件和其他器件的数据之间传输信息。SDA和SCL引脚都可以双向传输信号,在使用时都必须通过一个上拉电阻给其施加正电源电压。当总线空闲时,两引脚均为高电平。这两个引脚都采用漏极开路配置以实现线“与”操作。

1.I2C总线有两个主要的传输方式

标准模式:发送n个数据,n指的是I2C模块编程的数值。

重复模式:一直发送数据直到软件产生一个停止(STOP)条件或者一个新的启动(START)条件。

2.I2C模块的主要组成

1)一个串行接口:一个数据引脚SDA和一个时钟引脚SCL。

2)数据寄存器和FIFO:用于暂时保存SDA引脚和CPU之间接收或发送的传输数据。

图13-2 I2C模块结构框图(www.daowen.com)

3)控制和状态寄存器。

4)外设总线接口:用于使CPU访问I2C模块寄存器和FIFO。

5)时钟同步器:用于完成来自器件时钟发生器的I2C输入时钟和SCL引脚的时钟同步,在不同时钟频率下实现与主器件的同步数据传输。

6)分频预定标:将输入时钟分频产生I2C模块时钟。

7)噪声滤波器:对SDA和SCL引脚上的信号进行滤波。

8)仲裁模块:用于完成I2C模块(作为主模块)与其他主模块之间的仲裁处理。

9)中断产生逻辑:用于向CPU发送中断信号。

10)FIFO中断产生逻辑:可以使FIFO访问与I2C模块的数据接收和数据传输同步。

图13-2给出了在非FIFO模式下用于传输和接收的4个寄存器。在数据发送时,CPU向寄存器I2CDXR写数据;在接收数据时,CPU从寄存器I2CDRR中读数据。当I2C模块配置为发送器时,写入I2CDXR的数据被复制到寄存器I2CXSR,并逐位地移位到SDA引脚。当I2C模块配置为接收器时,接收的数据移位到寄存器I2CRSR,然后复制到I2CDRR。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。