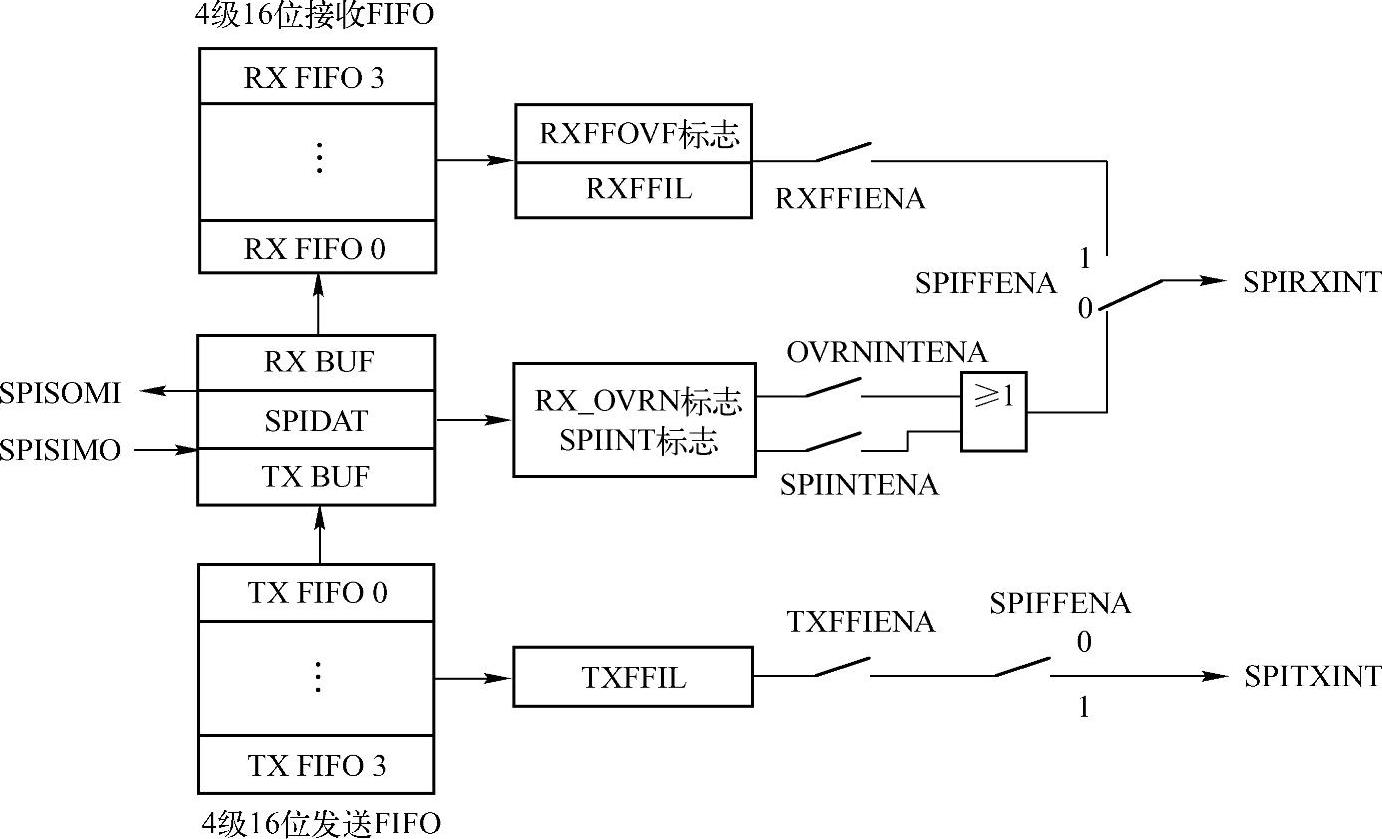

与24x芯片的SPI模块相比,2803x的SPI发送和接收各具有一个4级深的FIFO,并增加了延时发送控制。SPI FIFO中断标志和使能逻辑如图11-7所示。下面说明FIFO的特点以及SPI中断。

图11-7 SPIFIFO中断标志和使能逻辑

1)DSP复位时FIFO状态。在标准的SPI模式中,SPI上电复位时FIFO功能被禁止。FIFO的SPIFFTX、SPIFFRX和SPIFFCT寄存器都保持在无效状态。

2)标准SPI。标准SPI模式以SPIINT/SPIRXINT作为中断源进行工作。

3)模式改变。将SPIFFTX寄存器的SPIFFEN位置l可以使能增强型SPI FIFO模式。SPIRST可以在其操作的任何阶段复位FIFO模式。

4)激活寄存器。激活所有的SPI寄存器和SPI FIFO寄存器SPIFFTX、SPIFFRX及SPIFFCT。

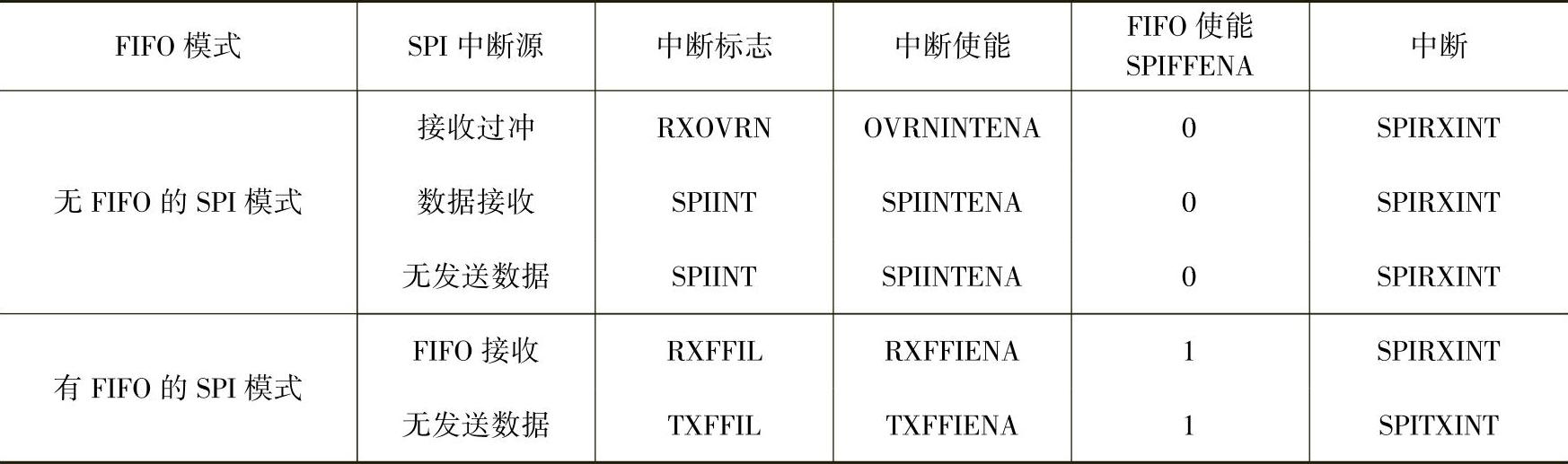

5)中断。SPI中断有4个相关的控制或标志位:SPI中断使能位SPIINTENA(SPICTL.0)、SPI中断标志位SPIINT(SPISTS.6)、溢出中断使能位OVERRUNENA(SPICTL.4)和接收溢出标志位OVERRUN(SPISTS.7)。

标准SPI接收到数据或者发送数据结束使用同一个标志位SPIINT,因为接收和发送由同一个移位寄存器SPIDAT完成。同时,SPIINT和接收溢出RX OVRN共用一个向CPU申请中断的请求线。FIFO模式具有两个中断请求线:一个用于发送FIFO的SPITXINT;另一个用于接收FIFO的SPIRXINT。SPIRXINT用于SPI FIFO的接收、接收错误和接收FIFO溢出等情况的中断。一旦使能FIFO模式(SPIFFENA=1),用于标准SPI发送和接收的SPLINT及溢出RX_OVRN中断将被禁止。(www.daowen.com)

当一个完整的字符移入或移出SPIDAT时,SPIINT中断标志位置位,如果中断使能则产生中断,中断确认可以清除标志位。CPU读SPIRXBUF、软件清0以及系统复位清除标志位。

6)缓冲器。发送和接收缓冲器将由两个4级16位的FIFO完成。标准SPI的1个字的发送缓冲器(SPITXBUF)作为发送FIFO和移位寄存器之间的过渡缓冲器。1个字的发送缓冲器只有在移位寄存器的最后一位被移出后才能被发送FIFO加载。

7)延迟传送。FIFO中的发送字被传输到发送移位寄存器的速度是可编程的。寄存器SPIFFCT中的FFXDLY7~FFXDLY0定义字传送之间的延迟。该延迟被定义为SPI串行时钟周期的数目。8位的寄存器可以定义最小延迟0而最大延迟为256个串行时钟周期。0延迟使SPI模块可以利用FIFO字以连续方式发送数据。可编程SPI的延迟简化了到各种慢速SPI外围的接口电路,如慢速EEPROM、ADC和DAC等。

8)FIFO状态位。发送和接收FIFO都有状态位TXFFST和RXFFST反映FIFO中可用字的数目。当发送FIFO复位位TXFIFO和接收FIFO复位位RXFIFO置1时,可将FIFO指针复位为0。当这些位清零时,FIFO将重新开始工作。

9)可编程中断级别。发送和接收都可以向CPU申请中断。当发送FIFO状态位TXFFST(位12~8)与中断触发级位TXFFIL(位4~0)相匹配(小于或等于)时,中断触发就会产生。这为SPI的发送和接收提供了一个可编程的中断级别。这些触发级别位的默认值对于接收是0x11111,而对于发送是0x00000。

SPI中断标志模式见表11-2。

表11-2 SPI中断标志模式

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。