【摘要】:SPI有4种时钟模式,由寄存器SPICCR中的时钟极性位CLOCK POLARITY和寄存器SPICTL的时钟相位位CLOCK PHASE控制。3)上升沿,无延时:SPI在时钟SPICLK上升沿发送数据,在下降沿接收数据。SPI时钟模式选择方法见表11-1,与发送和接收数据相对应的4种时钟模式如图11-5所示。当CLOCK PO-LARITY位被清零时,SPICLK的低电平比其高电平脉冲多一个CLKOUT时钟周期;当CLOCK POLARITY位被置1时,SPICLK的高电平比其低电平脉冲多一个CLKOUT时钟周期。图11-6 时钟SPICLK引脚的非对称特性

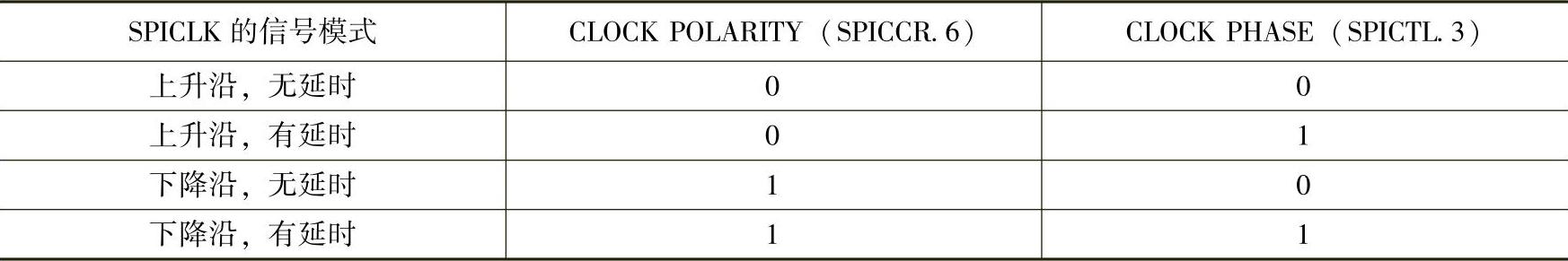

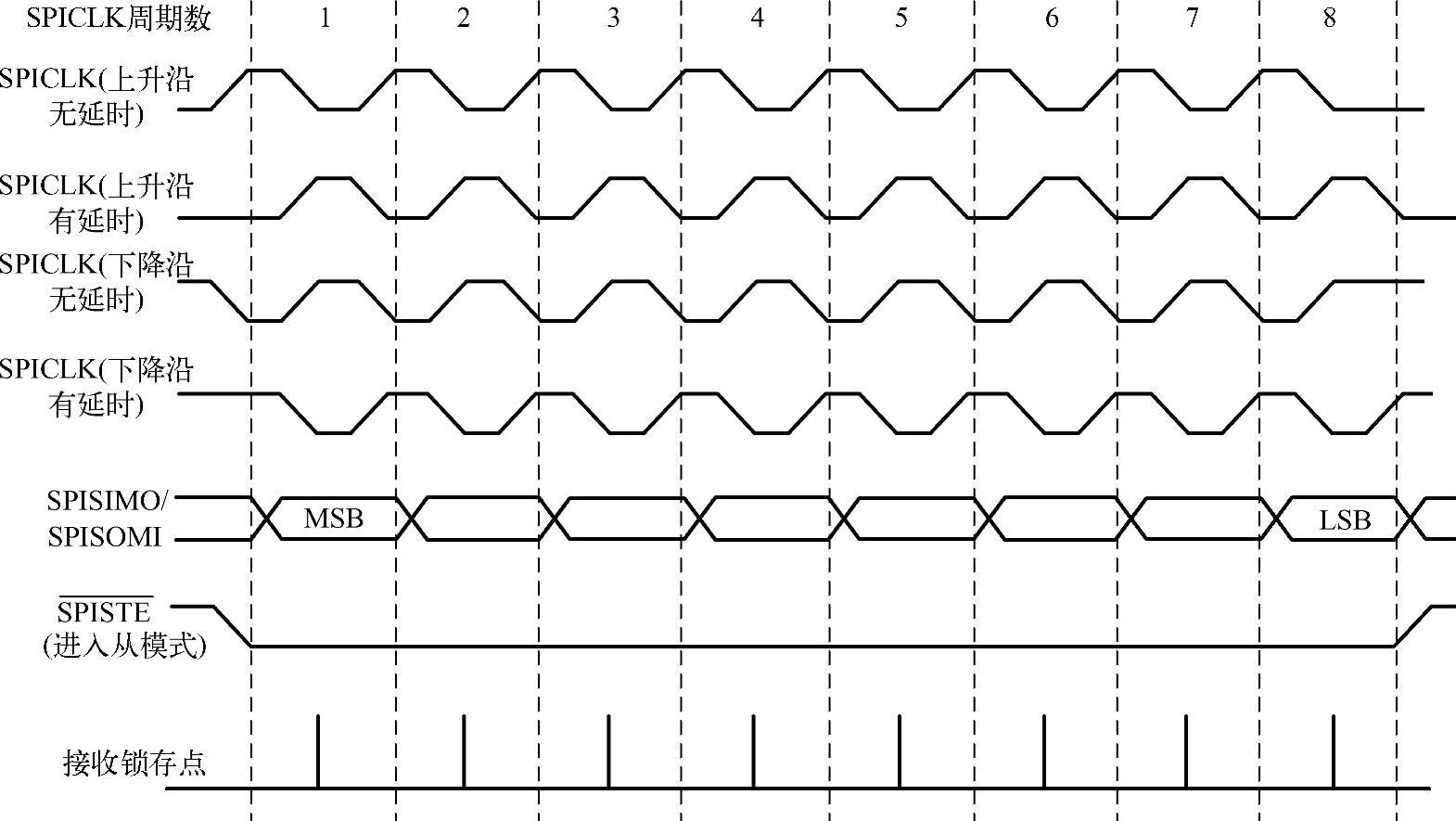

SPI有4种时钟模式,由寄存器SPICCR中的时钟极性位CLOCK POLARITY(SPICCR.6)和寄存器SPICTL的时钟相位位CLOCK PHASE(SPICTL.3)控制。CLOCK POLARITY位选择时钟的有效沿是上升沿还是下降沿;CLOCK PHASE位选择是否有半个时钟周期的延时。4种不同的时钟模式如下:

1)下降沿,无延时:SPI在时钟SPICLK下降沿发送数据,在时钟的上升沿接收数据。

2)下降沿,有延时:SPI在时钟SPICLK下降沿前半个周期发送数据,在时钟的下降沿接收数据。

3)上升沿,无延时:SPI在时钟SPICLK上升沿发送数据,在下降沿接收数据。

4)上升沿,有延时:SPI在时钟SPICLK上升沿前半个周期发送数据,在上升沿接收数据。

SPI时钟模式选择方法见表11-1,与发送和接收数据相对应的4种时钟模式如图11-5所示。

表11-1 SPI时钟模式选择方法(https://www.daowen.com)

图11-5 SPI时钟模式选择

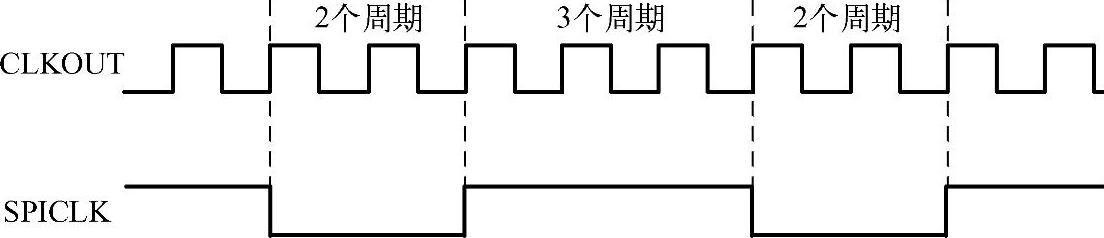

对于SPI,时钟SPICLK仅在(SPIBRR+1)的值为偶数时保持对称。当(SPIBRR+1)为奇数并且SPIBRR大于3时,SPICLK就会变为非对称,如图11-6所示。当CLOCK PO-LARITY位被清零时,SPICLK的低电平比其高电平脉冲多一个CLKOUT(即LSPCLK)时钟周期;当CLOCK POLARITY位被置1时,SPICLK的高电平比其低电平脉冲多一个CLKOUT时钟周期。

图11-6 时钟SPICLK引脚的非对称特性

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。

相关文章