数字比较子模块的运行由相应的寄存器控制与监测。这些寄存器包括:数字比较脱开选择寄存器DCTRIPSEL、数字比较A控制寄存器DCACTL、数字比较B控制寄存器DCBCTL、数字比较滤波控制寄存器DCFCTL、数字比较捕获控制寄存器DCCAPCTL、数字比较滤波偏移寄存器DCFOFFSET、数字比较滤波偏移计数器寄存器DCFOFFSETCNT、数字比较滤波窗口寄存器DCFWINDOW、数字比较滤波窗口计数器寄存器DCFWINDOWCNT以及数字比较计数器捕获寄存器DCCAP。

(1)数字比较事件

如前所述,脱开区输入和来自模拟比较器模块(COMP)的COMPxOUT信号可以通过DC⁃TRIPSEL位选择来产生数字比较器A高和低(DCAH/L)和数字比较器B高和低(DCBH/L)信号。那么TZDCSEL寄存器的配置限定了对选择的DCAH/L和DCBH/L信号的动作,该动作产生DCAEVT1/2和DCBEVT1/2事件(事件限定A和B)。

注意:当 信号被用作DCEVT脱开区功能时,被作为一个普通的输入信号并且可以定义为高有效或者低有效。当

信号被用作DCEVT脱开区功能时,被作为一个普通的输入信号并且可以定义为高有效或者低有效。当 、DCAEVTx.force、DCBEVTx.force信号有效时,EPWM输出异步触发脱开。为了使条件被锁存,至少需要3个TBCLK脉冲宽度。如果小于该宽度,脱开条件不一定能被CBC或者OST锁存器锁存。

、DCAEVTx.force、DCBEVTx.force信号有效时,EPWM输出异步触发脱开。为了使条件被锁存,至少需要3个TBCLK脉冲宽度。如果小于该宽度,脱开条件不一定能被CBC或者OST锁存器锁存。

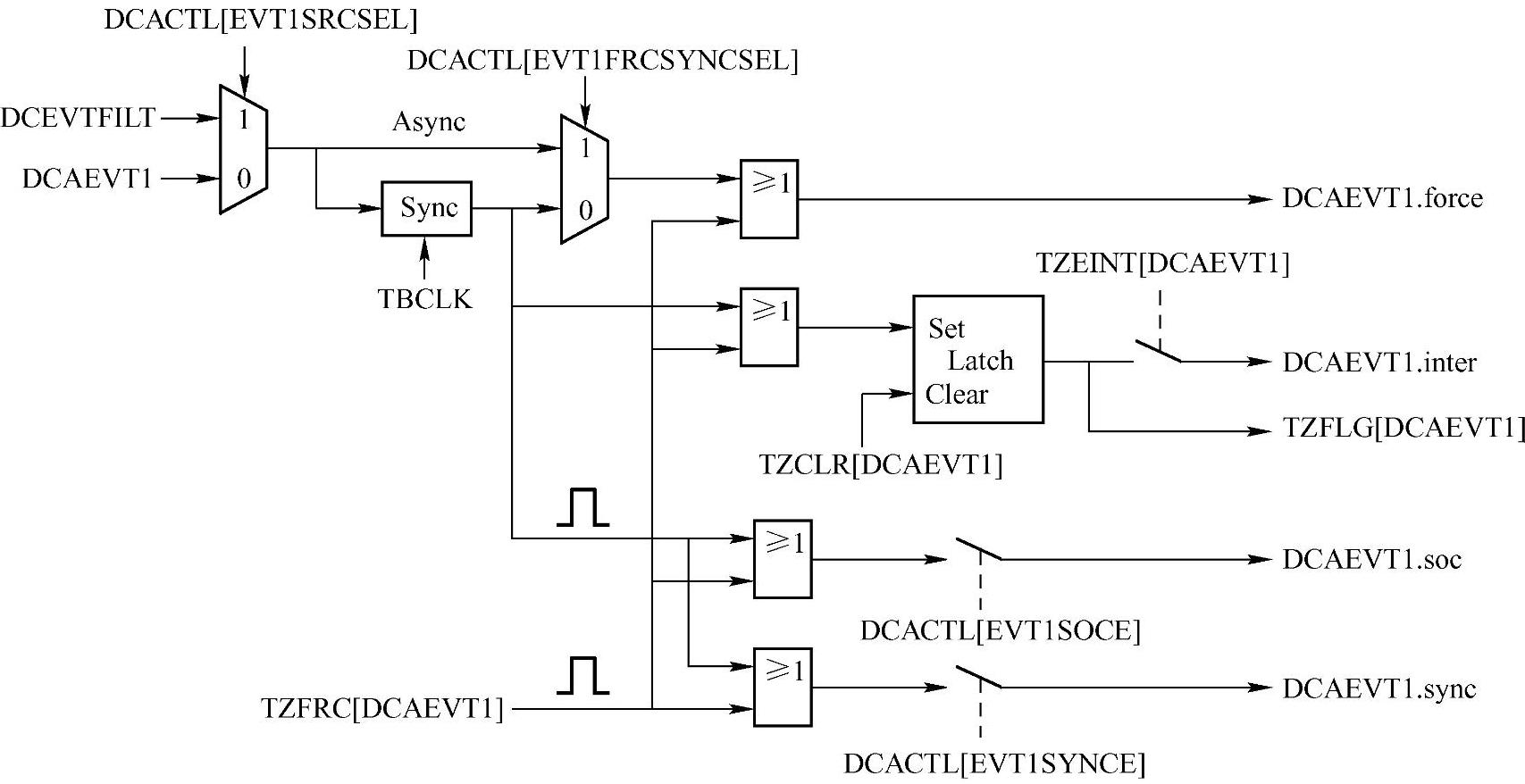

DCAEVT1/2和DCBEVT1/2事件可以被过滤,过滤后的事件就变成DCEVTFILT。过滤功能也可以旁路掉。DCAEVT1/2和DCBEVT1/2事件信号或者过滤得到的DCEVTFILT事件信号都可以产生强制信息到脱开区子模块、脱开区中断、ADC转换启动或者PWM同步信号。

1)强制信号。DCAEVT1/2.force信号是强制脱开条件,该条件可能直接影响EPWMxA引脚的输出(通过TZCTL[DCAEVT1或者DCAEVT2]配置),如果DCAEVT1/2信号被选择作为单触发或者周期脱开源(通过TZSEL寄存器),DCAEVT1/2.force信号能够通过TZCTL[TZA]配置影响脱开的动作。DCBEVT1/2.force信号的动作相似,但是它影响EPWMxB输出脚而不是EPWMxA。

TZCTL寄存器中冲突的动作的优先级如下(高优先级打断低优先级):

EPWMxA输出:TZA(最高)->DCAEVT1->DCAEVT2(最低)。

EPWMxB输出:TZB(最高)->DCBEVT1->DCBEVT2(最低)。

2)中断信号。DCAEVT1/2.interrupt信号产生到PIE的脱开中断。为了使能中断,用户必须置位TZEINT寄存器中的DCAEVT1、DCAEVT2、DCBEVT1或者DCBEVT2位。一旦这些事件有一个发生时,EPWMxTZINT中断就会被触发,TZCLR寄存器中相应的位必须置位才能清零中断。

3)SOC信号。DCAEVT1.soc信号与事件触发子模块连接并且可以通过ETSEL[SOCA-SEL]位作为产生ADC-A转换起始脉冲的事件。同样,DCBEVT1.soc信号可以通过ETSEL[SOCBSEL]位作为产生ADC-B转换起始脉冲的事件。

4)同步信号。DCAEVT1.sync和DCBEVT1.sync事件通过或门连接到EPWMxSYNCI输入信号并且TBCTL[SWFSYNC]信号产生到时基计数器的同步脉冲。(www.daowen.com)

如图7-14所示给出了DCAEVT1信号如何产生数字比较器A强制事件、中断、SOC和同步信号的框图。DCAEVT2、DCEVTFLT信号与DCAEVT1类似。

图7-14 DCAEVT1信号事件触发框图

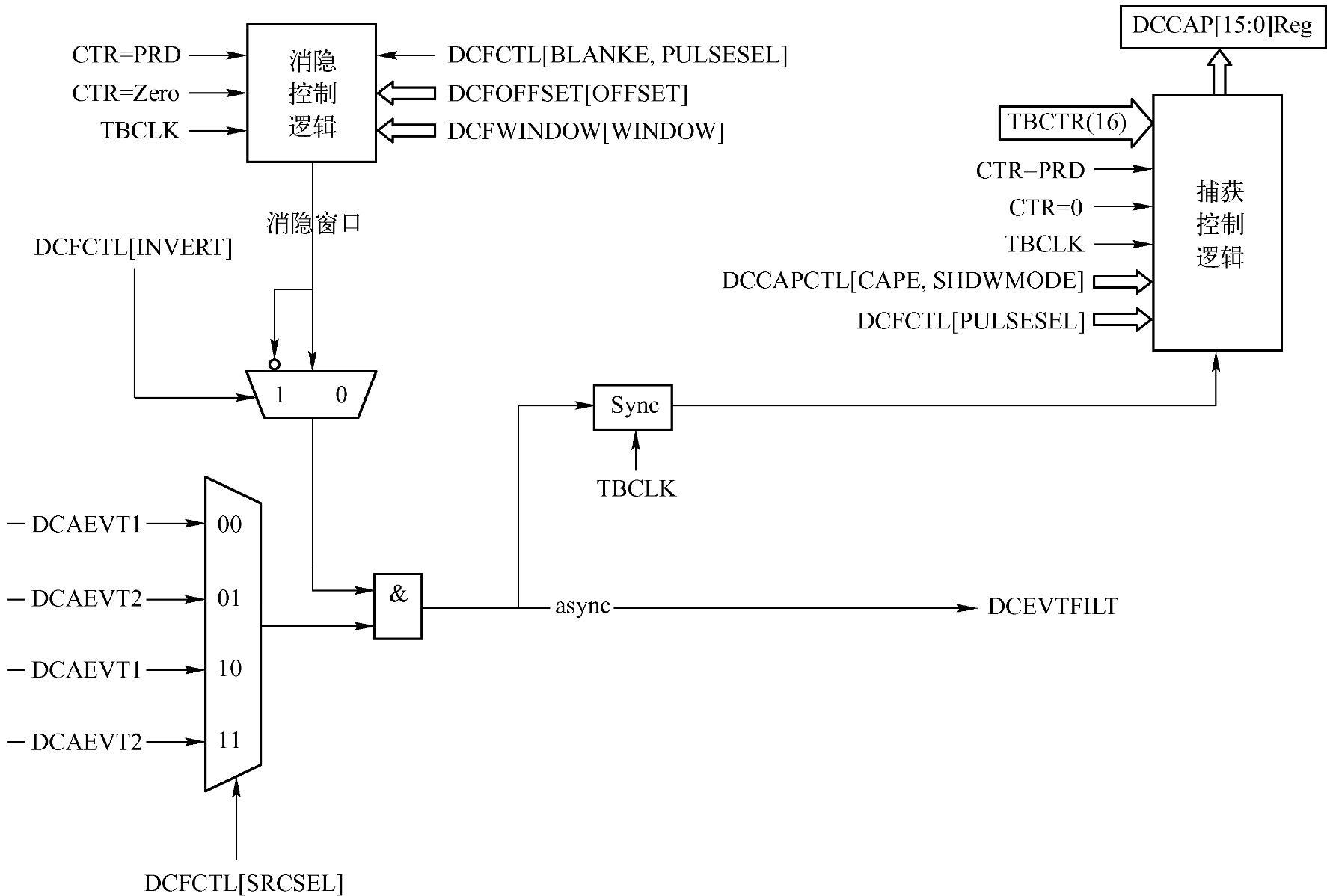

(2)事件滤波

DCAEVT1/2和DCBEVT1/2事件可以由事件过滤逻辑通过可选的消隐事件一定的周期数来除去噪声。当模拟比较器的输出被选择来触发DCAEVT1/2和DCBEVT1/2事件时,事件过滤很有用,消隐逻辑在驱动PWM输出或者产生中断或者ADC起始信号之前,可以过滤掉信号中潜在的噪声。事件过滤也可以捕获脱开事件的TBCTR值。图7-15给出了事件过滤逻辑的框图。

图7-15 事件过滤逻辑框图

如果消隐逻辑使能,数字比较事件DCAEVT1、DCAEVT2、DCBEVT1、DCBEVT2中的一个被选择要过滤。过滤掉所有的事件发生信号的消隐窗口将会和CTR=PRD脉冲或者CTR=0脉冲对齐(由DCFCTL[PULSESEL]位)。TBCLK计数的偏移值通过DCFOFFSET寄存器设置,该值决定了在CTR=PRD或者CTR=0脉冲之后的哪个点上启动裁剪窗口。裁剪窗口的持续时间,也就是偏移计数器记满之后的TBCLK计数值,由DCFWINDOW寄存器配置。在消隐窗口期间,所有的事件被忽略。在消隐窗口结束前后,事件可以像之前一样产生SOC(启动转换)、同步、中断和强制信号。

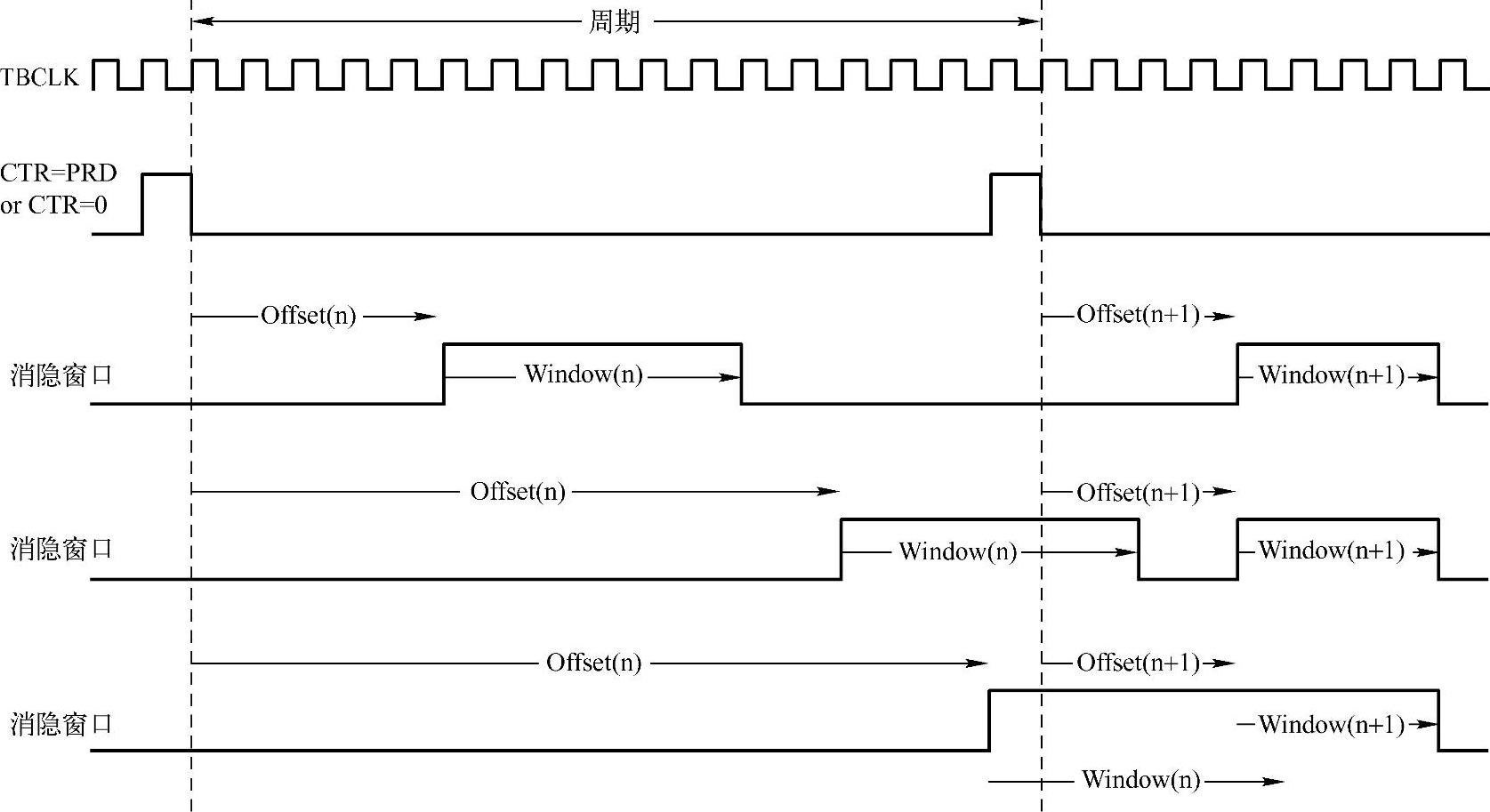

图7-16给出了几种偏移(Offset)和消隐窗口(Blank Window)的时序。注意,如果消隐窗口在CTR=0或者CTR=PRD边界交叉,下一个窗口仍然会在CTR=0或者CTR=PRD脉冲之后以同样的偏移值开始。

图7-16 消隐窗口时序

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。