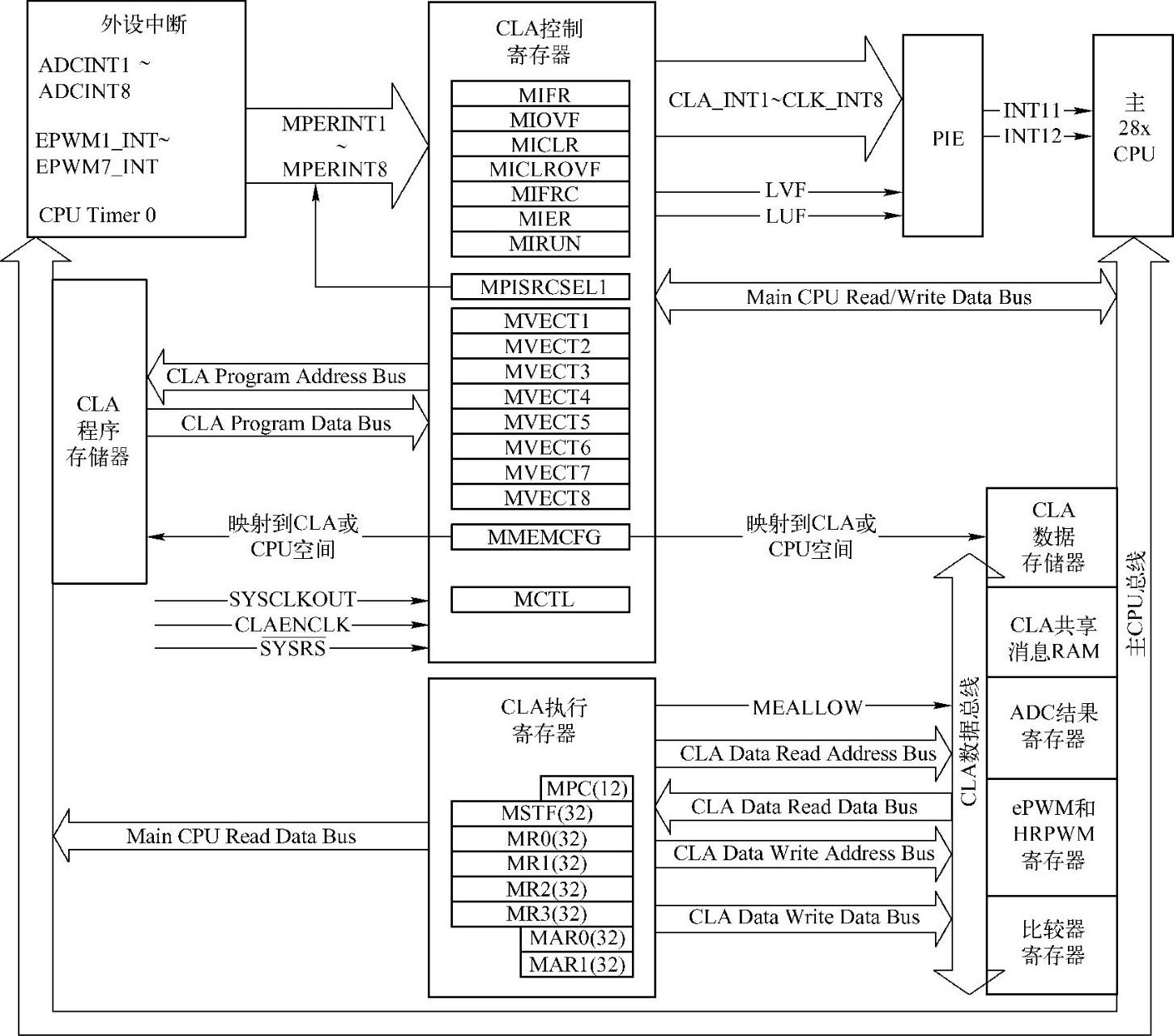

28035芯片具有一个控制律加速器(Control Law Accelerator,CLA),它是一个独立的32位浮点数学处理器,它为C28x CPU控制环的执行扩展了并行处理能力。CLA具有自己的总线结构、取指机制与流水线。可以指定8个CLA任务或子程序。每一个任务由软件或一个外设如ADC、ePWM或CPU定时器0启动。CLA在某一时间执行一个任务,任务完成时,由到PIE的中断通知主CPU,然后CLA自动开始下一个最高级的悬挂任务。CLA能直接访问ADC结果寄存器、ePWM+HRPWM寄存器。专门的消息RAM提供一个在主CPU和CLA之间传递附加数据的方法。通过将CLA用于时间要求严格的控制环,主CPU可以有更多的时间完成通信、诊断等系统任务。通过CLA可以实现更快的系统反应与更高的控制环频率。

控制律加速器有以下主要特点:

1)运行频率与主CPU一致(SYSCLKOUT)。

2)独立的、可编程32位浮点协处理器。

●它具完整的总线结构,包括程序地址总线、程序数据总线,数据地址总线、数据读总线、数据写总线。

●独立的8级流水线。

●12位程序计数器(MPC)。

●4个32结果寄存器(MR0~MR3)。

●两个16辅助寄存器(MAR0,MR1)。

●状态寄存器(MSTF)。

3)丰富的指令。

●IEEE单精度(32位)浮点数学运算。

●带有并行装入或存储的浮点数学运算。

●带有并行加法或减法的浮点乘法运算。

●1/x、1/sqrt(x)估算。

●数据类型转换。

●条件分支与调用。

●数据装入或存储操作。(https://www.daowen.com)

4)CLA程序代码可以由多达8个任务或中断服务程序组成。

●每个任务的开始地址由MVECT寄存器指定。

●只要可以放入CLA程序存储器空间,任务大小无限制。

●某一时间只能执行一个任务直到完成,不能进行任务嵌套。

●任务完成后,外设中断扩展模块PIE中设置相应的中断标志。

●在一个任务完成后,下一个最高优先级的悬挂任务自动开始。

5)任务触发机制。

●C28x CPU通过IACK指令。

●任务1~任务7:相应的ADC或ePWM模块中断。例如,任务1:ADCINT1或EP-WM1_INT,任务2:ADCINT2或EPWM2_INT,任务7:ADCINT7或EPWM7_INT。

●任务8:ADCINT8或CPU定时器0。

6)存储器与共享外设。

●两块专门的消息RAM用于主CPU和CLA之间的通信。

●C28xCPU可以将CLA程序和数据存储器映射到主CPU空间或CLA空间。

●CLA能直接访问ePWM+HRPWM寄存器、比较器和ADC结果寄存器。

CLA的结构框图如图6-1所示。

图6-1 CLA结构框图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。