每一个比较器模块包含一个10位DAC参考电压,它可以作为比较器的反相输入(B端)。DAC的电压输出可由DACVAL寄存器或一个下行斜波发生器(Ramp Down Generator)控制。

因为DAC也在模拟范围,所以为保持其输出电压不需要时钟。然而,为更改由DAC控制的数字输入需要时钟。

(1)DACVAL输入

当DACVAL寄存器被选为DAC输入时,DAC输出V由下式给出

式中,VDDA、VSSA为模拟电源电压值。

(2)斜波发生器输入

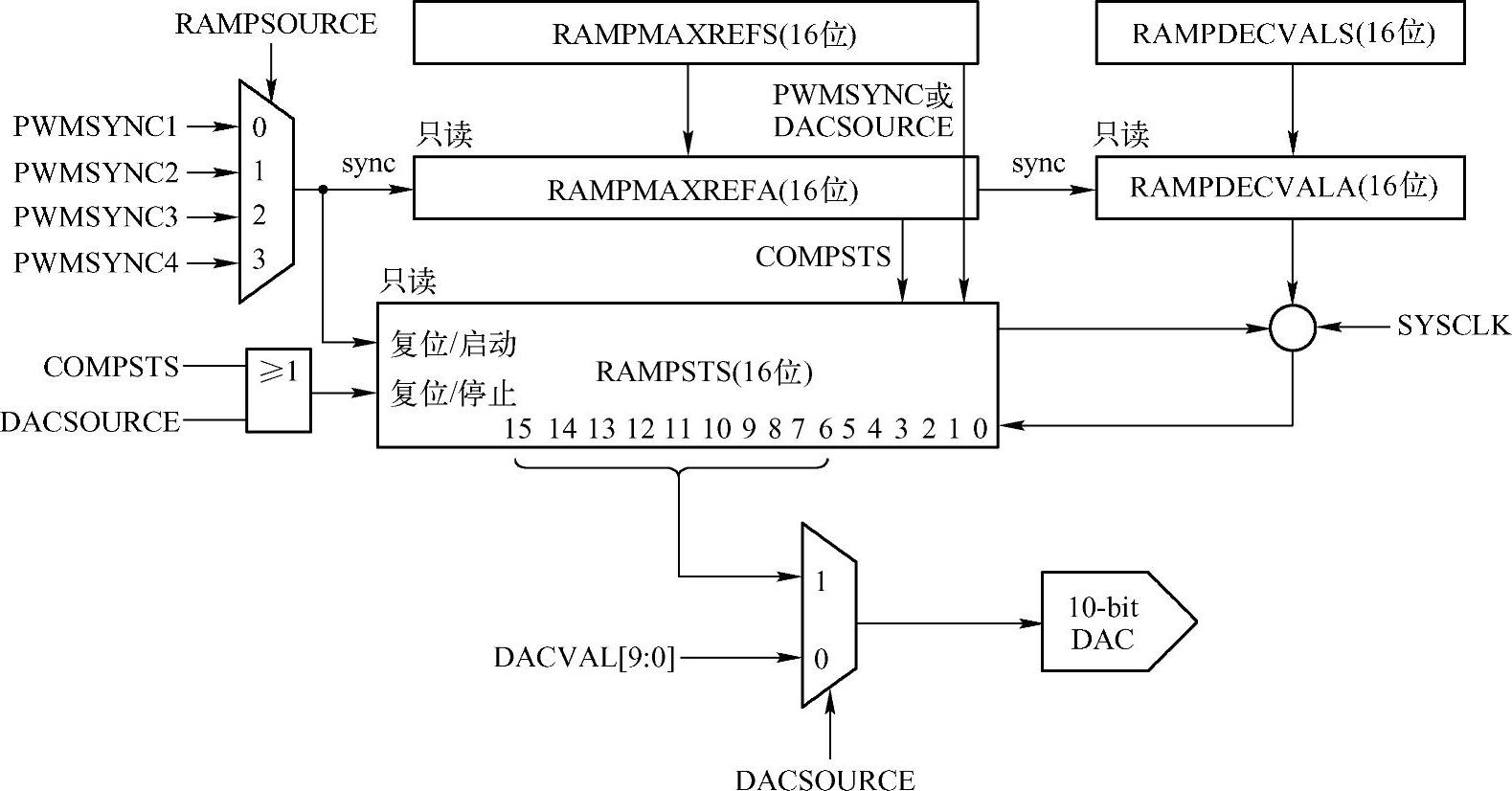

当选择斜波发生器输入时,斜波发生器可以产生一个下斜(Falling-ramp)的DAC输出信号。在该模式下,DAC采用16位向下计数寄存器RAMPSTS的高10位作为其输入。斜波发生器的框图如图5-12所示。

当接收到一个被选择的PWMSYNC信号时,RAMPSTS寄存器设置为RAMPMAXREF_SHDW的值,且从此后在每一个SYSCLK周期RAMPDECVAL_ACTIVE的值减去RAMPSTS。当通过设置DACSOURCE=1斜波发生器被刚一使能时,RAMPSTS寄存器的值由RAMPMAXREF_SHDW装入,且直到首次接到PWMSYNC信号时寄存器保持不变。(https://www.daowen.com)

当斜波发生器活跃时,如果COMPSTS为被比较器置1,RAMPSTS寄存器将复位到RAMPMAXREF_ACTIVE的值,且直到下一次接到PWMSYNC信号时保持不变。如果RAMP⁃STS的值到0,RAMPSTS寄存器保持0不变直到接到下一次PWMSYNC信号。

为减少在更新斜波发生器的RAMPMAXREFA和RAMPDECVALA值时出现竞争情况,只有影子寄存器RAMPMAXREF_SHDW和RAMPDECVAL_SHDW可以允许写入。在下一个PWMSYNC信号影子寄存器的复制到活跃寄存器。在同一个PWMSYNC信号周期,用户软件应避免再次写入影子寄存器,否则影子寄存器的值可能丢失。

为保证斜波发生器能够检测PWMSYNC信号,该信号的宽度必须大于SYSCLK。

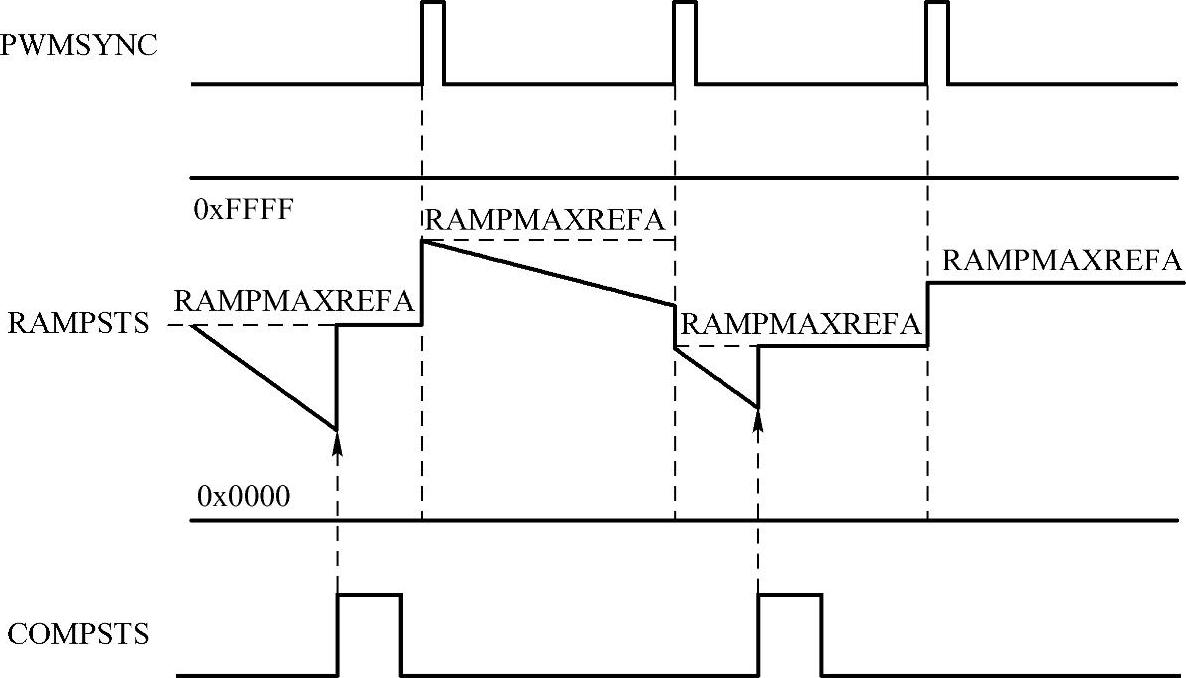

斜波发生器行为如图5-13所示。

图5-12 斜波发生器的框图

图5-13 斜波发生器行为

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。