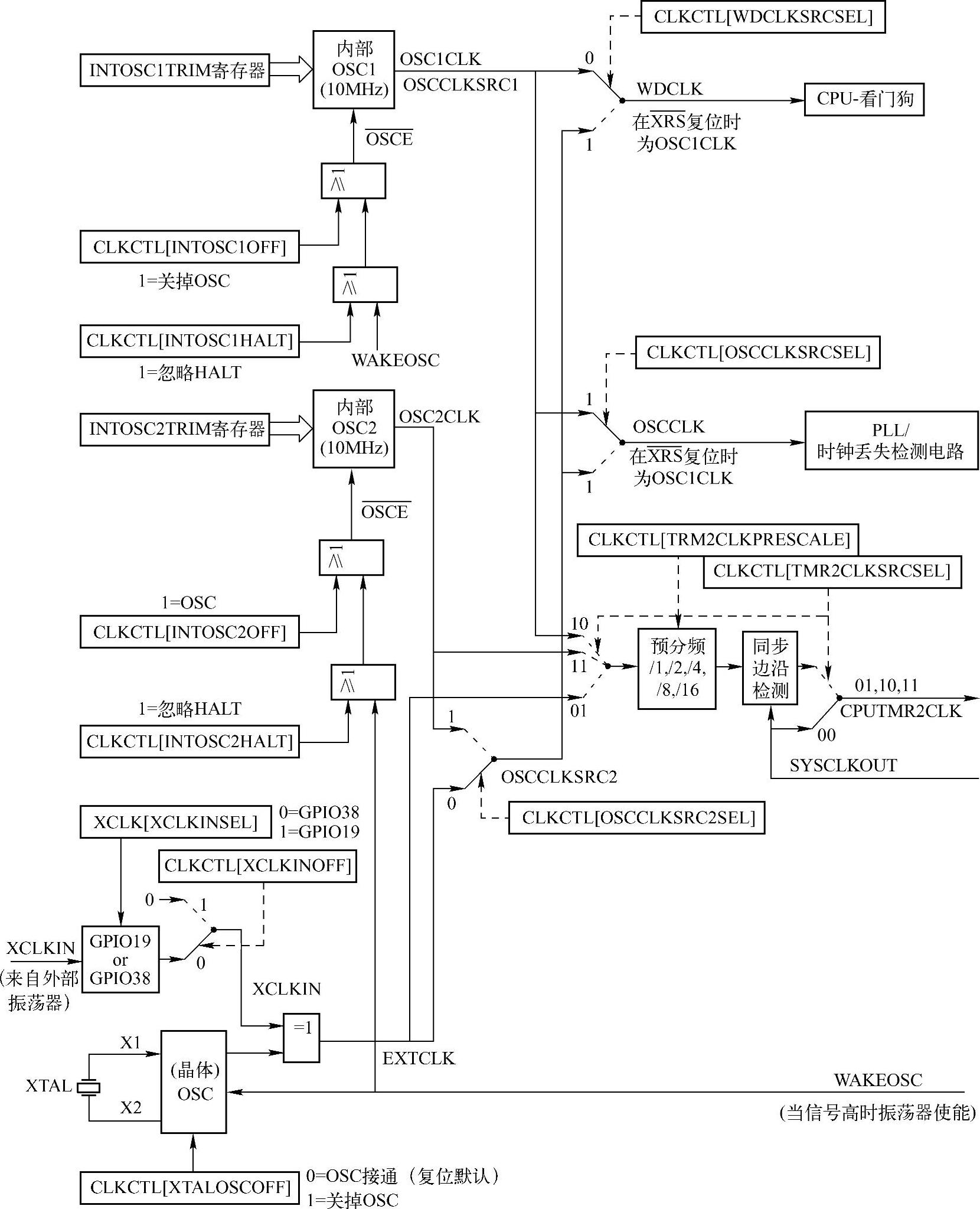

(1)输入时钟选择

2803x DSP片内振荡器(OSC)与锁相环(PLL)提供时钟信号,同时也可以用于低功耗模式。芯片内具有两个不需要外部元件的内部振荡器(INTOSC1、INTOSC2)。同时也有基于锁相环的片内时钟模块。输入时钟有4种选择:

1)INTOSC1(片内无引脚振荡器1)。它可以为看门狗、内核与CPU定时器2提供时钟。

2)INTOSC2(片内无引脚振荡器2)。它可以为看门狗、内核与CPU定时器2提供时钟。INTOSC2与INTOSC1都可以独立提供时钟。

3)晶体/谐振器工作方式。该模式下,外部无源晶振连接到DSP的X1和X2引脚上,DSP的振荡电路和无源晶振一起运行产生时钟,提供给DSP作为时间基准。

4)外部时钟工作方式。该模式下,不使用内部振荡器,即采用有源晶振,DSP的时钟来自XCLKIN引脚的外部时钟信号(注意XCLKIN与GPIO19或GPIO38引脚多功能复用)。可以通过寄存器XCLK的位XCLKSEL来选择GPIO19(复位默认值)或GPIO38作为XCLKIN输入。寄存器CLKCTRL的XCLKINOFF位禁止时钟输入(强制低)。如果不用外部时钟,用户可以在启动时禁止。

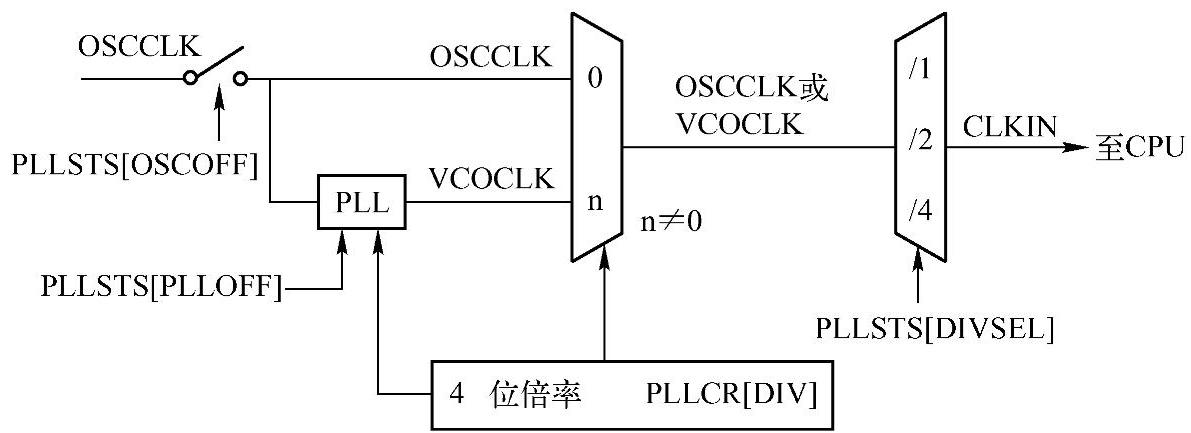

图2-8给出了2803x时钟选择电路。

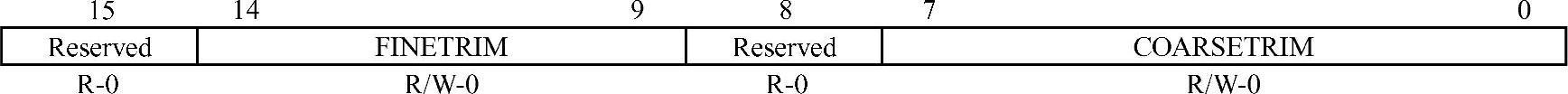

片内无引脚振荡器INTOSC1和INTOSC2的名义频率都是10MHz。两个16位寄存器IN⁃TOSC1TRIM和INTOSC2TRIM分别用于两个振荡器的修整(称为粗修),另外用软件的方法可以进行进一步修整(称为精修)。两个修整寄存器的用法一样。

修整寄存器INTOSC1TRIM或INTOSC2TRIM的格式如下。

位15、位8,保留位。

位14~9,FINETRIM:6位精修整值,有符号数(-31~+31)。

位7~0,CORSETRIM:8位粗修整值,有符号数(-127~+127)。

片内振荡器通过存储在OTP的参数进行软件修整。在引导时,引导ROM将数值复制到该寄存器。

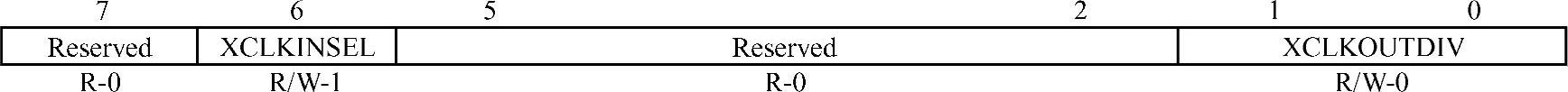

(2)配置输入时钟源与XCLKOUT选择

时钟寄存器XCLK用于选择XCLKIN输入的GPIO引脚并配置XCLKOUT引脚频率。其格式如下。

位15~7、位5~2,保留位。

位6,XCLKINSEL:XCLKIN输入源引脚选择位。

●0:选择GPIO38作为XCLKIN输入源引脚(该引脚也是JTAG的TCK)。

●1:选择GPIO19作为XCLKIN输入源(复位默认值)。

图2-8 时钟选择电路

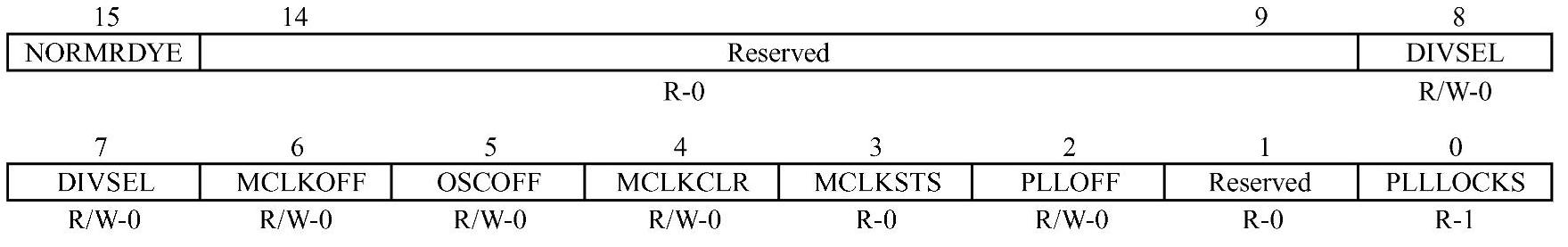

位1、位0,XCLKOUTDIV:XCLKOUT分频率。用于选择XCLKOUT相对于SYSCLK-OUT的分频率。

●00:XCLKOUT=SYSCLKOUT/4。

●01:XCLKOUT=SYSCLKOUT/2。

●10:XCLKOUT=SYSCLKOUT。

●11:关掉XCLKOUT。

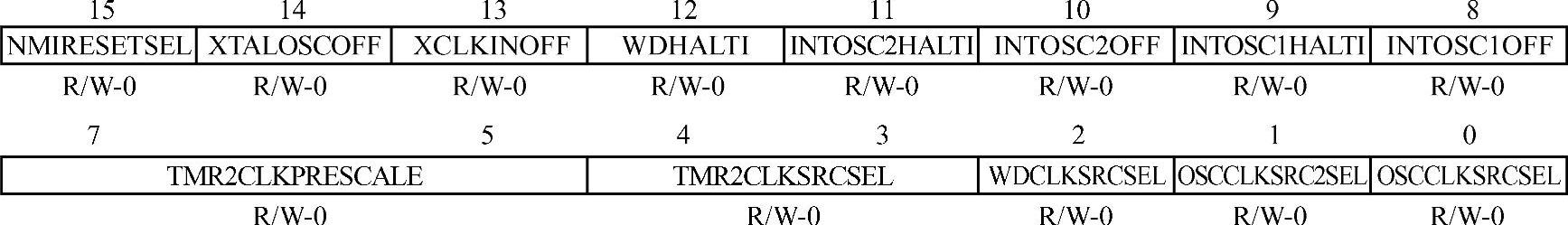

(3)配置器件时钟域

时钟控制寄存器CLKCTL选择可用的时钟源,并在时钟失效时配置器件。其格式如下。

位15,NMIRESETSEL:NMI复位选择位。该位用于选择当检测到丢失时钟情况时,是直接产生 信号还是用

信号还是用 信号复位。

信号复位。

●0:无延迟驱动MCLKRS(复位默认)。

●1:NMI看门狗复位 引发

引发 。

。

注意:产生CLOCKFAIL(时钟失效)信号与这种方式选择无关。

位14,XTALOSCOFF:该位用于是否关闭晶体振荡器。

●0:晶体振荡器接通(复位默认)。

●1:晶体振荡器关闭。位13,XCLKINOFF:XCLKIN关闭位。该位可关闭外部XCLKIN振荡器输入信号。

●0:XCLKIN振荡器输入接通(复位默认)。

●1:XCLKIN振荡器输入关闭。

注意:需要通过寄存器XCLK的XCLKINSEL位选择XCLKIN GPIO引脚。如果使用XCLKIN应将XTALOSCOFF设为1。

位12,WDHALTI:看门狗HALT(停止)模式忽略位。该位选择看门狗是否由HALT模式自动接通或关闭。这种特点可用于允许选择WDCLK时钟源在HALT模式下继续向看门狗提供时钟。这样可以使得看门狗能周期性的唤醒器件。

●0:看门狗由HALT模式自动接通或关闭(复位默认)。

●1:看门狗忽略HALT模式。

位11,INTOSC2HALTI:内部振荡器2 HALT模式忽略位。

该位选择内部振荡器2是否由HALT模式自动接通或关闭。此特点可用于允许内部振荡器2在HALT模式下继续提供时钟。这样可以更快从HALT模式唤醒。

●0:内部振荡器2由HALT模式自动接通或关闭(复位默认)。

●1:内部振荡器2忽略HALT模式。

位10,INTOSC2OFF:内部振荡器2关闭位。该位可关闭内部振荡器2。

●0:内部振荡器2接通(复位默认)。

●1:内部振荡器2关闭。该位可用于不使用时关闭内部振荡器2。该选择不受丢失时钟检测电路影响。

位9,INTOSC1HALTI:内部振荡器1 HALT模式忽略位。

该位选择内部振荡器1是否由HALT模式自动接通或关闭。该特点可用于允许内部振荡器2在HALT模式下继续提供时钟。这样可以更快从HALT模式唤醒。

●0:内部振荡器1由HALT模式自动接通或关闭(复位默认)。

●1:内部振荡器1忽略HALT模式。

位8,INTOSC1OFF:内部振荡器1关闭位。该位可关闭内部振荡器1。

●0:内部振荡器1接通(复位默认)。

●1:内部振荡器1关闭。该位可用于不使用时关闭内部振荡器1。该选择不受丢失时钟检测电路影响。

位7~5,TMR2CLKPRESCALE:CPU定时器2时钟定标值。这两位为选定的CPU定时器2时钟源选择定标值。该选择不受丢失时钟检测电路影响。

●000:/1(复位默认)。

●001:/2。

●010:/4。

●011:/8。

●100:/16。

●101~111:保留。

位4~3,TMR2CLKSRCSEL:CPU定时器2时钟源选择位。

●00:选择SYSCLKOUT(复位默认,旁路定标器)。

●01:选择外部振荡器。

●10:选择内部振荡器1。

●11:选择内部振荡器2。该选择不受丢失时钟检测电路影响。

位2,WDCLKSRCSEL:看门狗钟源选择位,选择WDCLK的来源。当 为低和在

为低和在 变高后,默认选择内部振荡器1。在初始化过程中,用户可能需要选择外部振荡器或内部振荡器2。如果丢失时钟检测电路检测到一个丢失时钟,该位被强制为0且选择内部振荡器1。用户改变该位不影响PLLCR寄存器的值。

变高后,默认选择内部振荡器1。在初始化过程中,用户可能需要选择外部振荡器或内部振荡器2。如果丢失时钟检测电路检测到一个丢失时钟,该位被强制为0且选择内部振荡器1。用户改变该位不影响PLLCR寄存器的值。

●0:选择内部振荡器1(复位默认)。

●1:选择外部振荡器或内部振荡器2。

位1,OSCCLKSRC2SEL:振荡器2时钟源选择位,用于选择是内部振荡器2还是外部振荡器。该选择不受丢失时钟检测电路影响。

●0:选择外部振荡器(复位默认)。

●1:选择内部振荡器2。

位0,OSCCLKSRCSEL:振荡器时钟源选择位,该位选择OSCCLK的来源。当 为低和在

为低和在 变高后,默认选择内部振荡器1。在初始化过程中,用户可能需要选择外部振荡器或内部振荡器2。

变高后,默认选择内部振荡器1。在初始化过程中,用户可能需要选择外部振荡器或内部振荡器2。

用户使用有关位无论什么时候改变时钟源,PLLCR寄存器将自动强制为0,这样可以避免潜在的PLL超调。然后用户必须写入PLLCR寄存器,以配置合适的分频系数。必要时用户还可以使用PLLLOCKPRD寄存器配置PLL锁定周期,以减少锁定时间。如果丢失时钟检测电路检测到丢失时钟,该位自动强制为0并选择内部振荡器1。PLLCR寄存器也将自动强制为0,以避免潜在的PLL超调。(https://www.daowen.com)

●0:选择内部振荡器1(复位默认)。

●1:选择外部振荡器或内部振荡器2。注意:如果希望内部振荡器2或外部振荡器为CPU提供时钟,应先配置该位,然后写到OSCCLKSRCSEL位。

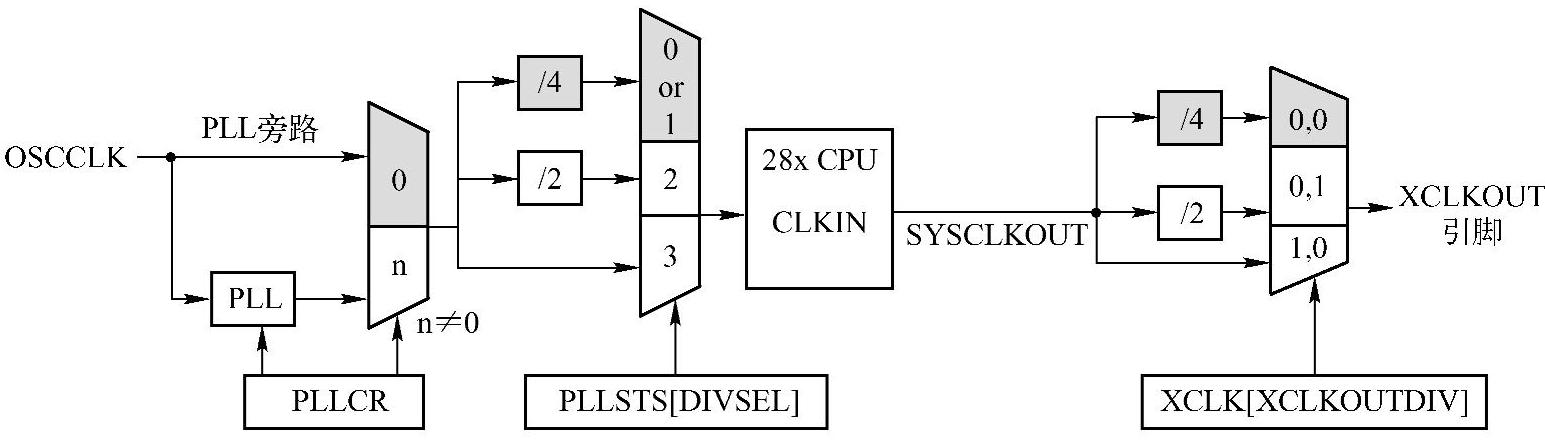

(4)基于锁相环的时钟模块

图2-9所示为振荡器(OSC)与锁相环(PLL)模块图。

图2-9 OSC与PLL模块

当使用XCLKIN作为外部时钟源时,具有X1和X2引脚的器件应将X1接低电平而X2悬空。

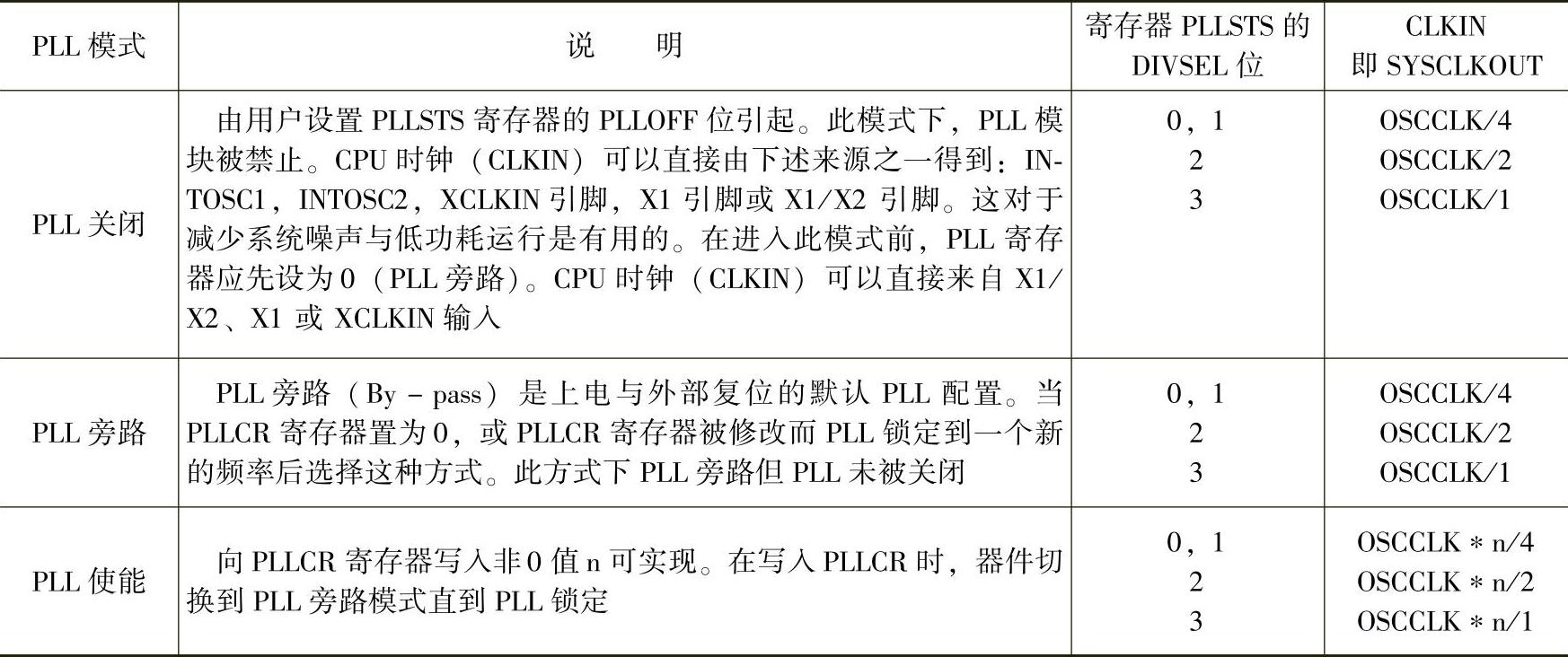

锁相环可能的配置模式见表2-9。

表2-9 锁相环(PLL)可能的配置模式

(5)输入时钟失效检测

DSP的内部或外部时钟源有可能失效。当PLL没有被禁止时,主振荡器失效逻辑允许器件检测这种情况并默认为一个已知的状态。

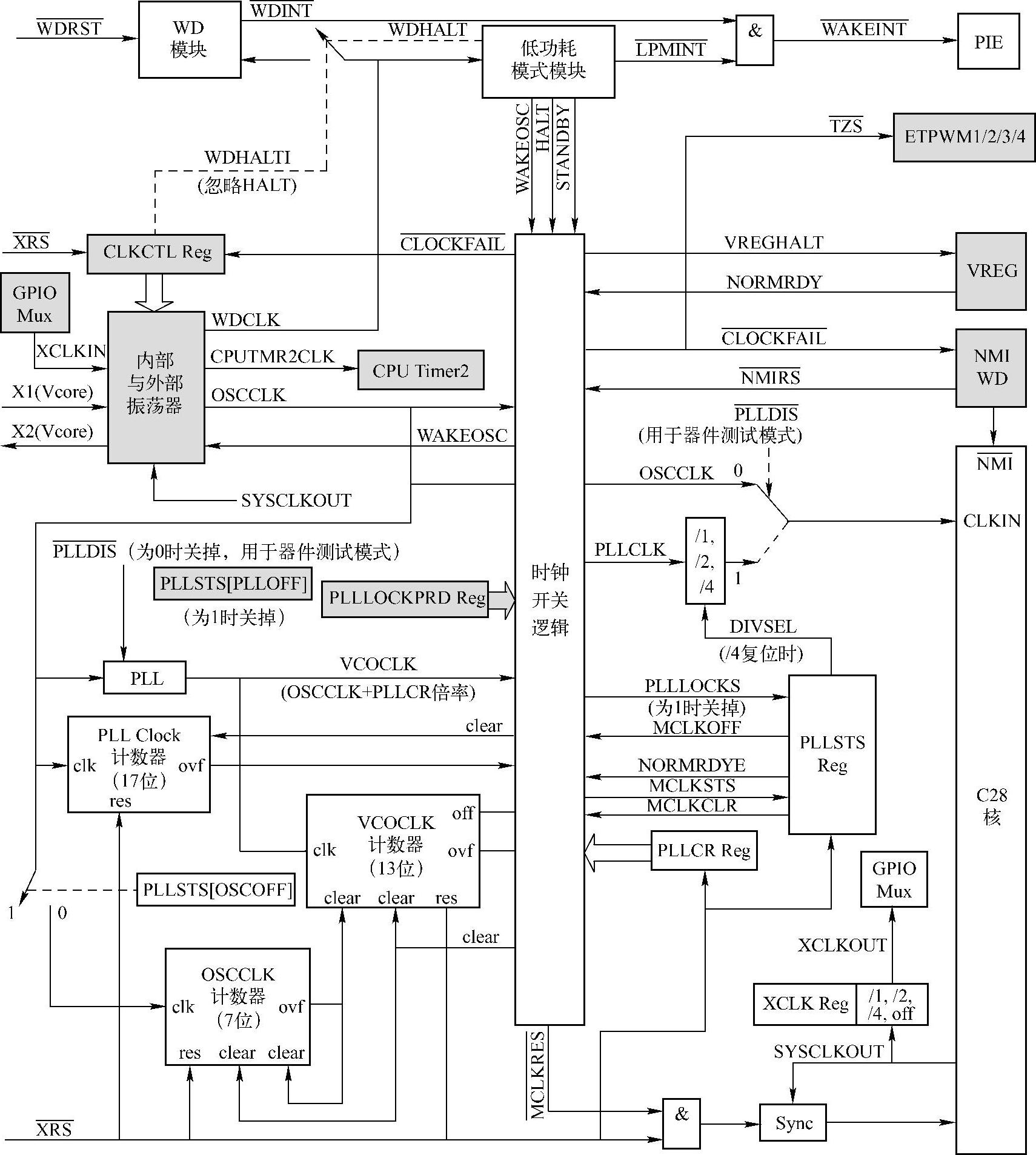

两个计数器用于监测OSCCLK信号的存在,如图2-10所示。第一个计数器由OSCCLK信号自己递增。当PLL没有被关闭时,第二个计数器由来自于PLL模块的VCOCLK信号递增。两个计数器这样配置:当7位OSCCLK计数器溢出时,清除13位VCOCLK计数器。在正常运行模式,只要OSCCLK信号存在,VCOCLK计数器永远不会溢出。

如果OSCCLK信号丢失,PLL将输出一个默认的跛行(Limp)模式频率,VCOCLK计数器将继续递增。自从OSCCLK丢失后OSCCLK计数器不再递增,因此VCOCLK计数器不周期性清零。最后,VCOCLK计数器溢出,器件将到CPU的CLKIN输入切换到PLL的跛行模式输出频率。

图2-10 振荡器逻辑电路

当VCOCLK计数器溢出时,丢失时钟检测逻辑复位CPU、外设和其他器件逻辑。产生的复位被称为丢失时钟检测逻辑复位 。

。 只是一个内部复位。器件的外部复位引脚

只是一个内部复位。器件的外部复位引脚 未被

未被 拉低,而且PLLCR和PLLSTS寄存器也未被复位。除了复位器件,丢失振荡器逻辑还设置寄存器PLLSTS的MCLKSTS位。当

拉低,而且PLLCR和PLLSTS寄存器也未被复位。除了复位器件,丢失振荡器逻辑还设置寄存器PLLSTS的MCLKSTS位。当 为1时,表明丢失振荡器逻辑已经复位器件且CPU正在跛行模式频率运行。

为1时,表明丢失振荡器逻辑已经复位器件且CPU正在跛行模式频率运行。

软件应当在复位后检测寄存器PLLSTS的MCLKSTS位,以确定器件是否因为丢失时钟情况由 复位。

复位。 置位后,固件应当采取合适的动作例如系统关闭。向寄存器PLLSTS的MCLKSTS位写1,可以清除丢失时钟状态。这样将复位丢失时钟检测电路和计数器。如果写入MCLKCLR位后,若OSCCLK仍然丢失,VCOCLK计数器会再次溢出且过程将重复。

置位后,固件应当采取合适的动作例如系统关闭。向寄存器PLLSTS的MCLKSTS位写1,可以清除丢失时钟状态。这样将复位丢失时钟检测电路和计数器。如果写入MCLKCLR位后,若OSCCLK仍然丢失,VCOCLK计数器会再次溢出且过程将重复。

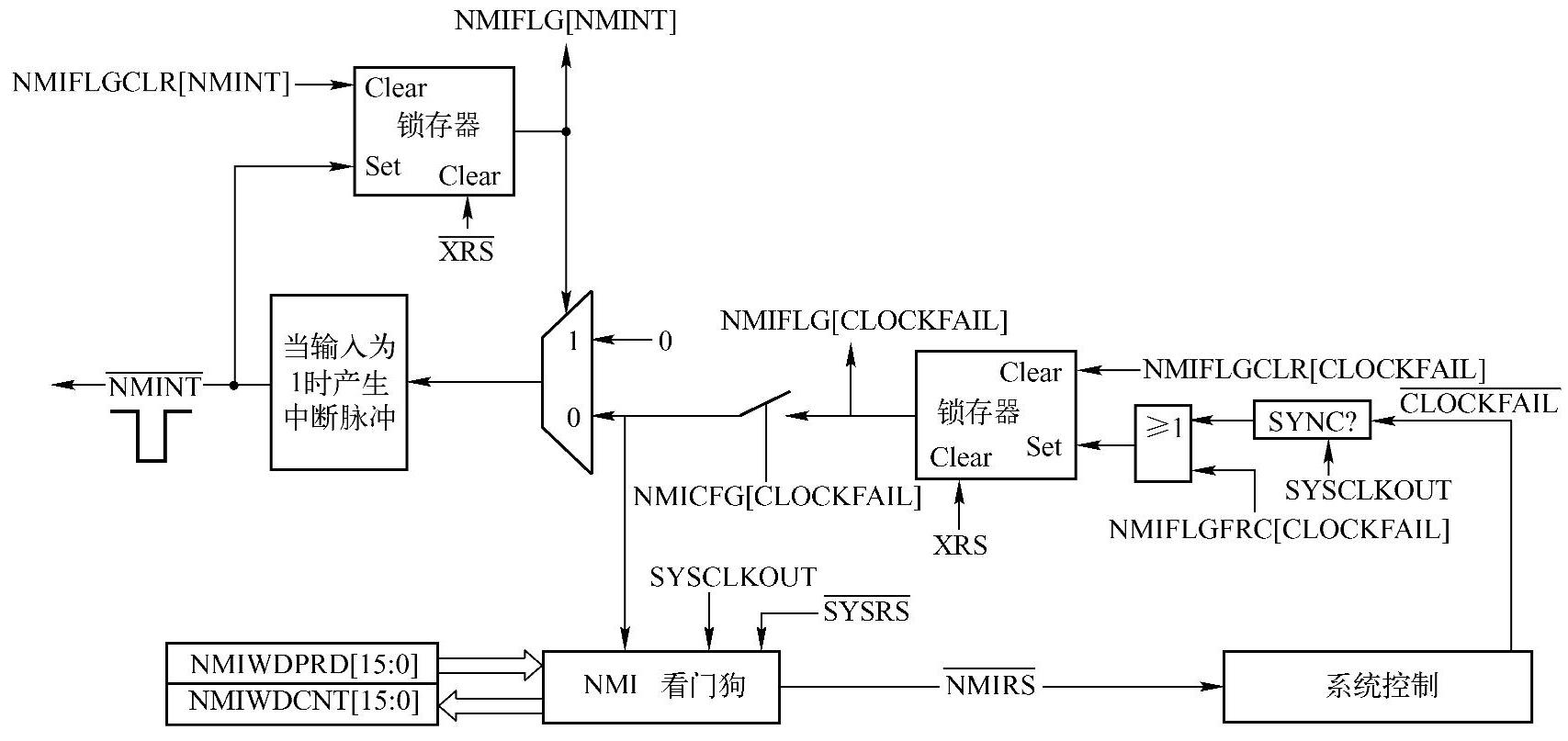

(6)NMI中断与NMI看门狗

NMI看门狗(NMIWD)用于检测并帮助从时钟失效情况恢复。NMI中断使能系统中出错的CLOCKFAIL(时钟失效)情况监测。在280x/2833x/2823x器件中,当检测到丢失时钟时,会立即产生一个丢失时钟复位 。然而在Piccolo器件中,首先产生一个CLOCKFAIL信号,它被送到NMI看门狗电路,然后经过一个可编程的延时产生一个复位。然而该特征在上电是不使能的,即当Piccolo器件刚上电时,与其他28xx一样,时钟失效立即产生

。然而在Piccolo器件中,首先产生一个CLOCKFAIL信号,它被送到NMI看门狗电路,然后经过一个可编程的延时产生一个复位。然而该特征在上电是不使能的,即当Piccolo器件刚上电时,与其他28xx一样,时钟失效立即产生 信号。用户必须通过CLKCTL寄存器的NMIRESETSEL位使能CLOCKFAIL信号的产生。注意此NMI看门狗只用于时钟失效情况,与下节所述的看门狗是不同的。

信号。用户必须通过CLKCTL寄存器的NMIRESETSEL位使能CLOCKFAIL信号的产生。注意此NMI看门狗只用于时钟失效情况,与下节所述的看门狗是不同的。

当OSCCLK丢失时,CLOCKFAIL信号触发NMI并使NMIWD计数器运行。在NMI中断服务程序中(ISR),程序将采取校正动作(例如切换到一个替代的时钟源)、清除CLOCK⁃FAIL信号和和NMIINT标志。如果未这样做,NMIWDCTR将溢出并经过若干个预先编程的SYSCLKOUT周期产生NMI复位 。

。

NMIRS传递到MCLKRS产生一个返回到内核的系统复位。其目的是在复位产生以前,允许软件合理关闭系统。注意NMI复位并没有反映到 引脚,对器件来说是内部复位。

引脚,对器件来说是内部复位。

CLOCKFAIL信号也可以用于激活TZ5信号,以将PWM引脚驱动到高阻状态。这样允许PWM输出在时钟失效时被停止(Triped)。图2-11给出了CLOCKFAIL(时钟失效)中断机制。NMI中断与NMI看门狗通过寄存器NMICFG、NMIFLG、NMIFLGCLR、NMIFLGFRC、NMIWDCNT及NMIWDPRD管理,可参见相关英文手册[3]。

图2-11 时钟失效中断

(7)XCLKOUT产生

XCLKOUT信号来自于系统时钟SYSCLKOUT,如图2-12所示。XCLKOUT可以与SY-SCLKOUT相等,也可以是其1/2或1/4。上电复位默认,XCLKOUT=SYSCLKOUT/4=OSC-CLK/16。

图2-12 XCLKOUT产生电路

XCLKOUT信号不用的话,将寄存器XCLK的XCLKOUTDIV位域设置为3,可以将其关闭。

(8)锁相环控制寄存器、状态寄存器与锁相环锁定周期寄存器

锁相环控制寄存器(PLLCR)用于改变锁相环的倍频系数。在写入PLLCR寄存器之前,应满足以下要求:PLLSTS[DIVSEL]位必须为0(使能CLKIN/4)。只有PLL完成锁定后,即PLLSTS[PLLLOCKS]=1,才改变PLLSTS[DIVSEL]位。

一旦PLL稳定且锁定新的指定频率,PLL将CLKIN切换到新的数值。这时,PLLSTS寄存器的PLLLOCKS位设置为1,表明PLL已完成锁定,且器件已运行在新的频率。用户软件通过监控PLLLOCKS位,以确定PLL什么时间完成锁定。一旦PLLSTS[PLLLOCKS]=1,就可以改变DIVSEL位。

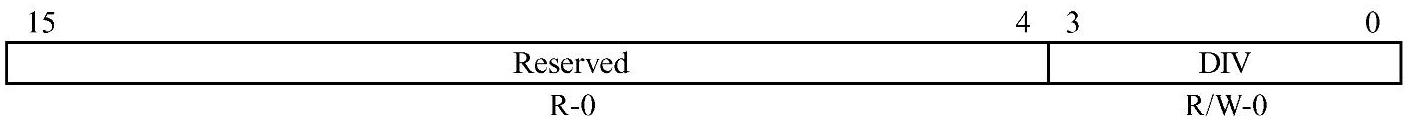

锁相环控制寄存器PLLCR(PLL Control Register)的格式为

●位15~4,保留。

●位3~0,DIV定标系数位。该位设置PLL是否直通,或不直通时的PLL倍频系数n。若最低4位DIV=0000(复位默认值),PLL直通即不经过PLL。若DIV=0001~1100,则PLL倍频系数n=1~12。DIV=1101~1111保留。锁相环的设置见表2-10。

表2-10 锁相环的设置

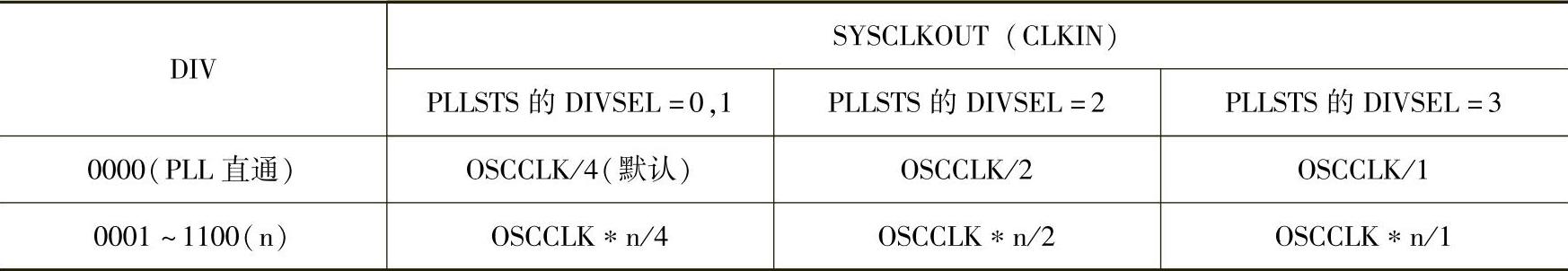

锁相环状态寄存器PLLSTS(PLL Status Register)的格式如下。

位15,NORMRDYE:NORMRDY信号使能位。

该位选择当电压调节器VREG失去调节时,来自VREG的NORMRDY信号是否阻止PLL接通。可以用于当进入和退出HALT模式时,保持PLL关闭。

●0:NORMRDY信号不阻止PLL(PLL忽略NORMRDY信号)。

●1:NORMRDY信号阻止PLL(当NORMRDYPLL低时,PLL关闭)。当VREG失去调节时,NORMRDY信号为低。如果VREG在调节范围,该信号为高。位14~9、位1,保留位。位8、7,DIVSEL:分频选择位。这两位选择到CLKIN的分频系数,可以选择4,2,1分频。

●00、01:4分频。

●10:2分频。

●11:1分频。

位6,丢失时钟检测关闭位。

●主振荡器失效检测逻辑使能(默认)。

●主振荡器失效检测逻辑禁止且PLL不发出跛行模式时钟。当不能受检测电路影响时使用这种方式,例如在外部时钟关闭时。

位5,OSCOFF:振荡器时钟关闭位。

●0:来自于X1,X1/X2或XCLKIN的OSCCLK信号连接到PLL模块(默认)。

●1:来自于X1,X1/X2或XCLKIN的OSCCLK信号不连接到PLL模块。这并不关闭内部振荡器。该位用于测试丢失时钟检测逻辑。当OSCOFF位置1时,不要进入HALT(停止)或STANDBY(备用)模式,或写入PLLCR寄存器,因为这样的操作能导致不可预测的行为。

当OSCOFF位置1时,看门狗的行为因为所使用输入时钟源(X1,X1/X2或XCLKIN)的不同而有差异:

●X1或X1/X2:看门狗不起作用。

●XCLKIN:看门狗起作用应当在设置OSCOFF之前禁止。

位4,MCLKCLR:丢失时钟清除位。

●0:写0无影响。读总为0。

●0:强迫丢失时钟检测电路清零和复位。如果OSCCLK时钟仍然丢失,检测电路会向系统产生一个复位,设置丢失时钟状态位(MCLKSTS),这时将会由PLL提供CPU跛行模式频率。

位3,MCLKSTS:丢失时钟状态位。

在复位后检测该位的状态,以确定是否检测到丢失时钟条件。在正常条件下,该位为0。写入此位被忽略。写入MCLKCLR位或强制外部复位,将清零该位。

●0:表明正常运行。没有检测到丢失时钟条件。

●1:表明检测到OSCCLK丢失。主振荡器失效检测逻辑将复位器件,CPU由PLL跛行模式频率提供时钟。

位2,PLLOFF:PLL关闭位。该位关闭PLL。可用于系统噪声测试。只有PLLCR寄存器为0时,才可以使用此方式。

●0:PLL接通(默认)。

●1:PLL关闭。当该位置1时,PLL模块将保持掉电。

在该位写1前,器件应处于PLL旁路模式(PLLCR=0x0000)。在PLL关闭(PLLOFF=1)时,不要向PLLCR写入非零值。

当PLLOFF=1时,应当工作于STANDBY或HALT低功耗模式。从低功耗模式唤醒后,PLL模块将保持掉电。

位0,PLL锁定状态位。

●0:表明PLLCR已写入数值且PLL正在锁定。CPU锁定到OSCCLK/2直到PLL锁定。

●1:表明PLLCR已完成锁定,正稳定运行。

16位锁相环锁定周期寄存器PLLLOCKPRD存放锁相环锁计数周期值。其中的16位数值是可编程的。当其中的数值为FFFFh~0000h时,表示锁相环锁定周期为65535~0个OS-CCLK周期。复位默认值为65535。

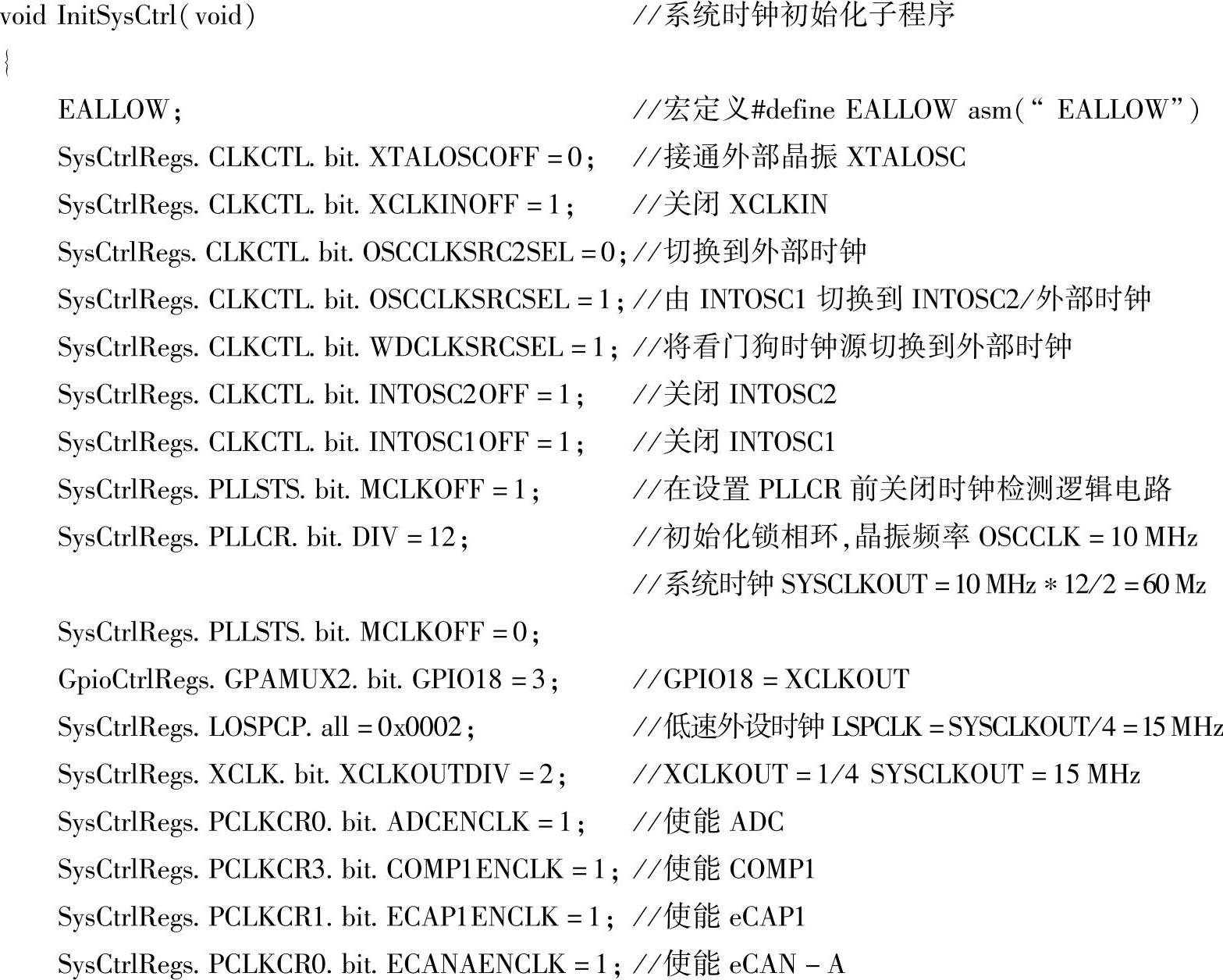

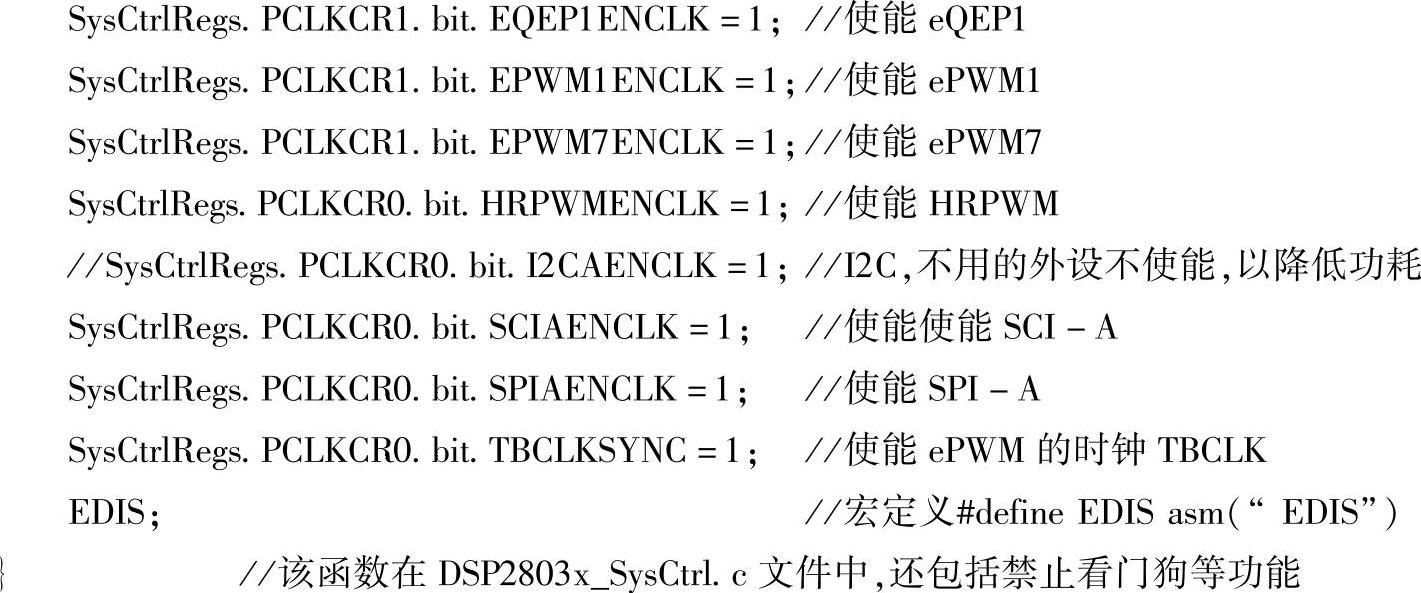

例2-2 时钟模块和锁相环初始化C语言程序段。

这里片内外设寄存器通常采用结构体的方法进行访问,具体方法见第4章。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。