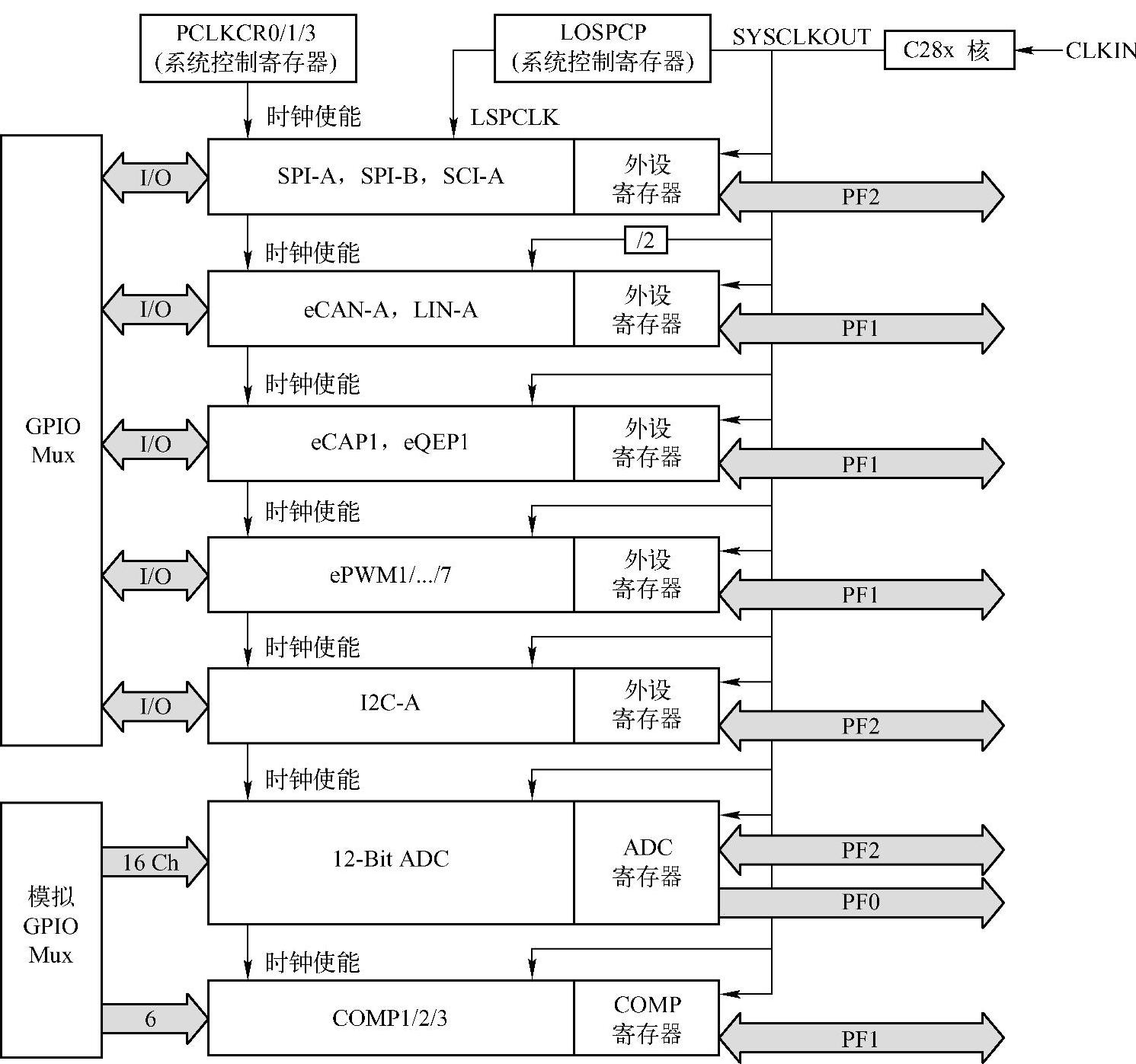

图2-7给出了2803x不同外设的时钟电路。

图中,CLKIN是输入到CPU的时钟信号,未作处理就直接从CPU输出成为系统时钟SYSCLKOUT信号,二者频率相等,即SYSCLKOUT=CLKIN。

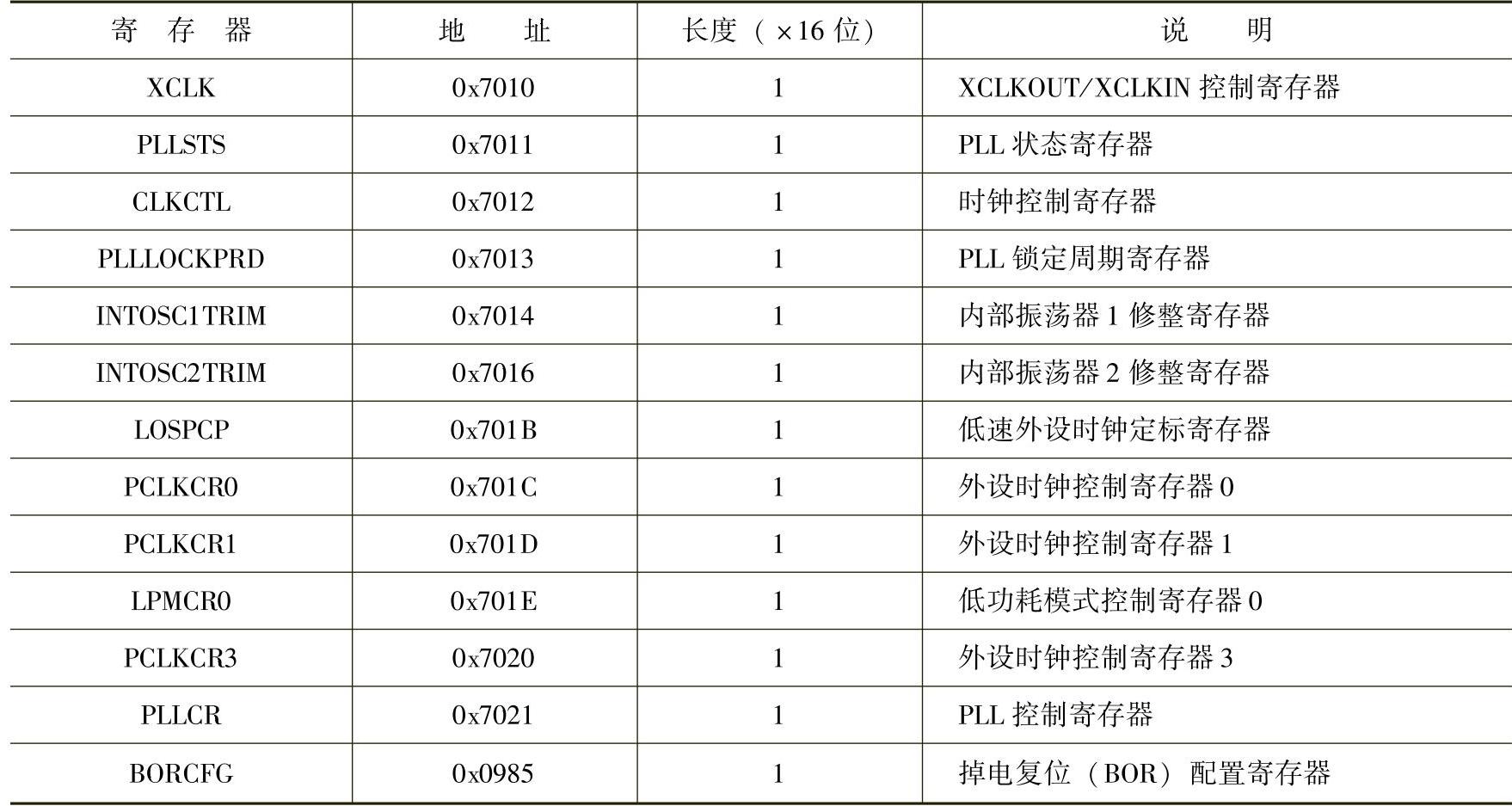

表2-8给出了锁相环(Phase locked Loop,PLL)、时钟、低功耗模式的相关寄存器。

图2-7 外设的时钟电路

表2-8 锁相环、时钟、低功耗模式寄存器

下面介绍时钟寄存器的定义及使用方法。

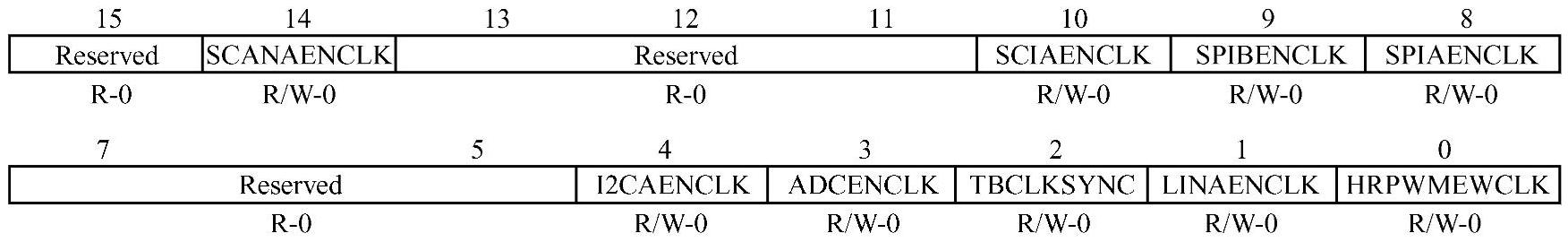

(1)外设时钟控制寄存器0(PCLKCR0)

外设时钟控制寄存器PCLKCR0/1/3用于使能或禁止各种外设模块的时钟。PCLKCR0的格式如下。

●位15、位13~11、位7~5,保留。

●位14,ECANENCLK:若设为1,则使能CAN外设中的系统时钟SYSCLKOUT/2。否则禁止(复位默认)。

●位10,SCIAENCLK:若设为1,则使能SCI-A外设中的低速时钟LSPCLK。

●位9,SPIBENCLK:若设为1,则使能SPI-B外设中的低速时钟LSPCLK。

●位8,SPIAENCLK:若设为1,则使能SPI-A外设中的低速时钟LSPCLK。

●位4,I2CAENCLK:若设为1,则使能I2C模块的时钟。

●位3,ADCENCLK:若设为1,则使能ADC外设中的时钟。

●位2,TBCLKSYNC:ePWM模块时间基准时钟(Time Base Clock,TBCLK)同步。允

许用户所有使能的ePWM模块都与TBCLK同步。

若设为0,各使能的ePWM模块的TBCLK停止。若寄存器PCLKCR1中的ePWM时钟使能位为1,即使TBCLKSYNC为0,ePWM模块仍然由SYSCLKOUT提供时钟。

若设为1,所有使能的ePWM模块时钟由TBCLK的第一个启动信号对齐。为完全同步各TBCLK,寄存器TBCLK中的定标位应设为一致。使能ePWM模块时钟的合适步骤是:

①使能寄存器PCLKCR1中的ePWM时钟。

②将TBCLKSYNC位设为0。

③配置定标值与ePWM模式。

④将TBCLKSYNC位设为1。

●位1,LINAENCLK:若设为1,则使能LIN外设中的时钟。(https://www.daowen.com)

●位0,HRPWMENCLK:若设为1,则使能HRPWM外设的时钟。

如果不使用某个外设,可将相应的时钟使能位设为0,屏蔽相应的时钟信号,禁止该外设工作,从而降低DSP功耗。上电复位后所有位均为0,即默认状态为所有外设均不工作。

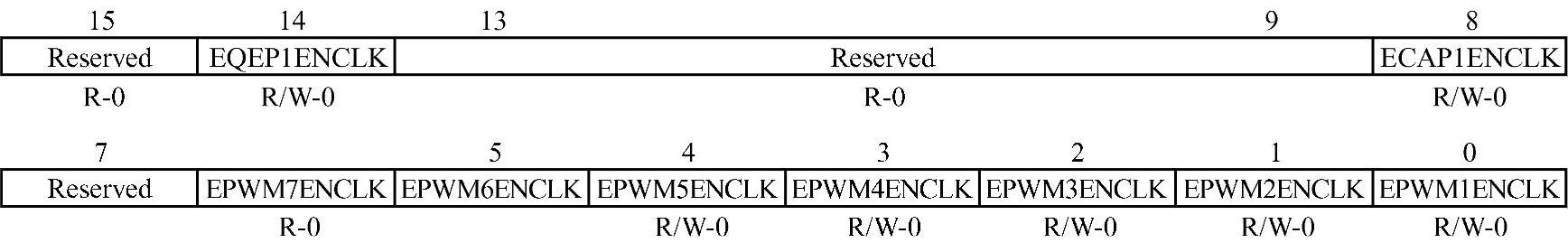

(2)外设时钟控制寄存器1(PCLKCR1)

●位15、位13~9、位7,保留。

●位14,EQEP1ENCLK:eQEP1时钟使能位。若设为1,则使能eQEP1模块中的系统时钟(SYSCLKOUT),否则禁止(复位默认)。

●位8,ECAP1ENCLK:eCAP1时钟使能位。若设为1,则使能eCAP1模块中的系统时钟(SYSCLKOUT),否则禁止(复位默认)。

●位6,EPWM7ENCLK:ePWM7时钟使能位。若设为1,则使能ePWM7模块中的系统时钟(SYSCLKOUT),否则禁止(复位默认)。

●位5~0,EPWM6ENCLK~EPWM1ENCLK:ePWM6~ePWM1的时钟使能位。若相应位设为1,则使能相应模块中的系统时钟(SYSCLKOUT),否则禁止(复位默认)。注意该寄存器受EALLOW保护。

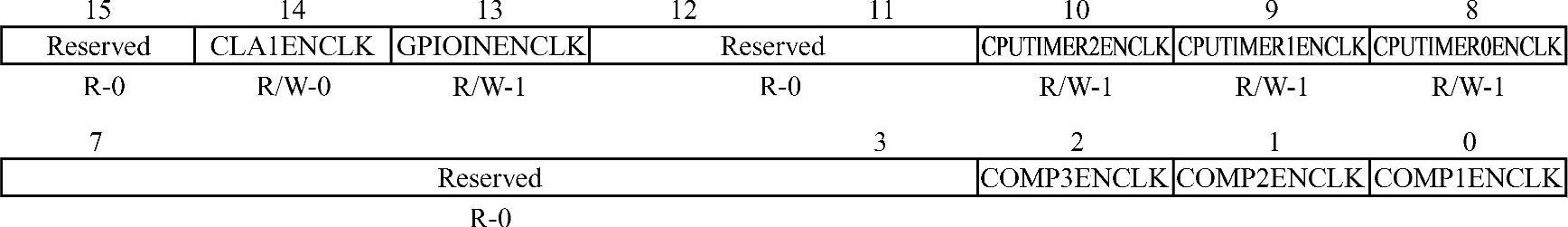

(3)外设时钟控制寄存器3(PCLKCR3)

●位15、位12~11、位7~3,保留。

●位14,CLA1ENCLK:CLA模块时钟使能位。若设为1,则使能CLA模块时钟,否则禁止。

●位13,GPIOINENCLK:GPIO输入时钟使能位。若设为1,则使能GPIO模块时钟,否则禁止。

●位10,CPUTIMER2ENCLK:CPU定时器2时钟使能位。若设为1,则使能CPU定时器2时钟,否则禁止。

●位9,CPUTIMER1ENCLK:CPU定时器1时钟使能位。若设为1,则使能CPU定时器1时钟,否则禁止。

●位8,CPUTIMER0ENCLK:CPU定时器0时钟使能位。若设为1,则使能CPU定时器0时钟,否则禁止。

●位2,CMP3ENCLK:比较器3时钟使能位。若设为1,则使能比较器3时钟,否则禁止。

●位1,CMP2ENCLK:比较器2时钟使能位。若设为1,则使能比较器2时钟,否则禁止。

●位0,CMP1ENCLK:比较器1时钟使能位。若设为1,则使能比较器1时钟,否则禁止。

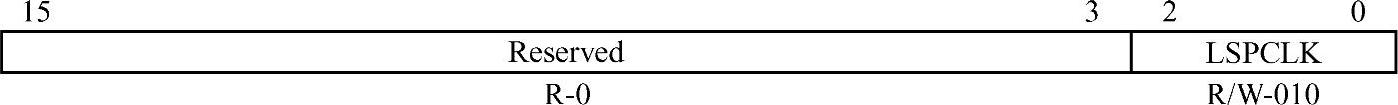

(4)低速外设时钟定标寄存器(LOSPCP,Low Speed Peripheral Clock Prescaler)

●位15~3,保留。

●位2~0,LSPCLK,低速外设时钟定标位。用于对SYSCLKOUT分频,产生低速外设时钟LSPCLK。

若最低3位LOSPCP2~0不为0,则LSPCLK=SYSCLKOUT/(2×LOSPCP2~0)。复位时,默认值为010,则LSPCLK=SYSCLKOUT/4。

若LOSPCP2~0=0,则LSPCLK=SYSCLKOUT。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。