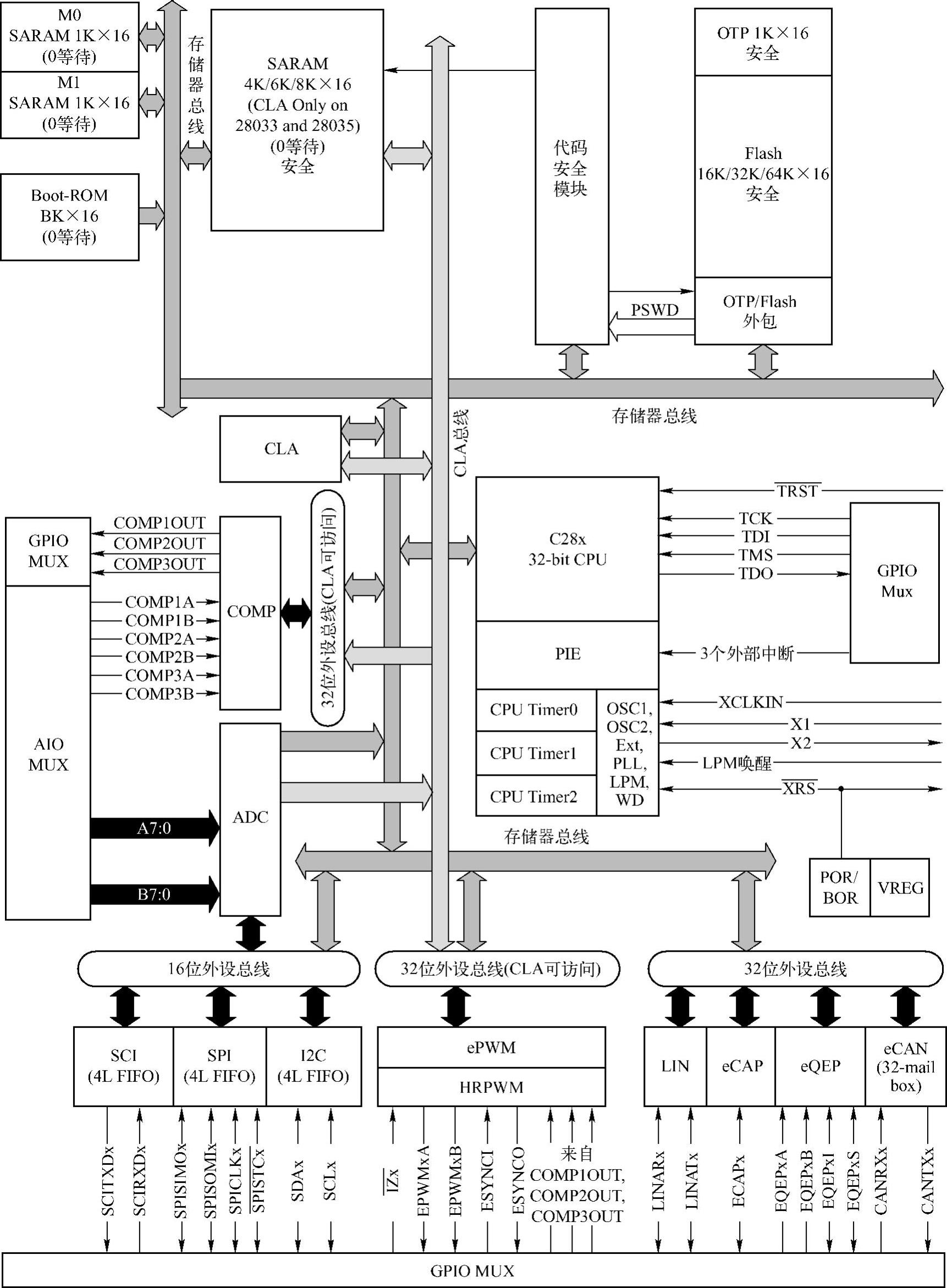

2803x DSP控制器功能框图如图2-4所示。它由C28x 32位CPU、片内存储器以及片内外设等组成。

图2-4 2803x的功能框图

2803x系列是C2000 MCU(微控制器)平台的一个成员。该系列与其他28x器件具有同样的32位定点CPU。

28035芯片还具有一个控制律加速器(Control Law Accelerator,CLA)。它是一个单精度(32位)浮点单元,为C28x CPU扩展并行处理能力。CLA是一个独立的处理器,具有自己的总线结构、取指机制与流水线。可以指定8个CLA任务或子程序。每一个任务由软件或一个外设如ADC、ePWM或CPU定时器0启动。CLA在某一时间执行一个任务。任务完成时,由到PIE的中断通知主CPU,然后CLA自动开始下一个最高级的悬挂任务。CLA能直接访问ADC结果寄存器、ePWM+HRPWM寄存器。专门的消息RAM提供一个在主CPU和CLA之间传递附加数据的方法。

图2-5所示为28034/28035的存储器映射图。对该图的说明如下:

1)外设帧(Peripheral Frame,PF)0、1、2的存储器只被映射到数据存储器,用户程序不能在程序存储空间访问这些存储器。

2)被保护(Protected)存储空间指写之后的读操作不按流水线顺序进行而是被保护起来。

3)一些存储器范围受EALLOW保护,以防配置好后任意改写。

4)存储单元0x3D 7C80~0x3D 7CC0包含内部振荡器与ADC校准程序,这些单元用户不能编程。

5)CLA专用寄存器和RAM只适用于28035器件。

外设帧1、2可以被“写/读外设块保护”。这里“保护”模式确保了这些块的写操作。由于28x流水线设计的原因,如果在写操作后立即跟着读不同的存储器地址,将使CPU存储器总线的顺序改变,这可能带来问题。28x的CPU支持块保护模式,即一个区域块可以被保护起来,确保了写操作的进行,缺点是带来了额外的处理时间。该模式是可编程的,默认状态是保护被选择的区域。

28035的Flash存储器的地址范围是0x3E 8000~0x3F 7FFF,即容量为64KW。

2803x有多种引导(Boot)模式,常用的引导模式是Flash模式。这时引导程序跳转到Flash存储器的0x3F7F F6地址,开始执行此处的用户程序。用户需要在0x3F 7FF6地址放好一条跳转指令,使程序继续跳转到其他地方执行。

2803x具有4MW存储空间,包括数据、程序空间。片内存储器包括:

✔1KW的SARAM M0(00 0000~00 03FFH)。SARAM(Single Access RAM)为单访问RAM。(https://www.daowen.com)

1KW的SARAM M1(00 0400~00 07FFH)。复位时堆栈指针指向M1块的开始。M0块、M1块与其他C28x器件的存储器块一样,被同时映射到程序与数据空间。因此M0和M1块可用于存储代码或数据变量,其分配在链接器中完成。C28x器件为编程者提供一个统一的存储器映射,使得用高级语言编程更方便。

1KW的SARAM M1(00 0400~00 07FFH)。复位时堆栈指针指向M1块的开始。M0块、M1块与其他C28x器件的存储器块一样,被同时映射到程序与数据空间。因此M0和M1块可用于存储代码或数据变量,其分配在链接器中完成。C28x器件为编程者提供一个统一的存储器映射,使得用高级语言编程更方便。

2KW片内外设PF0(00 0800~00 0CFFH)。

2KW片内外设PF0(00 0800~00 0CFFH)。

256W的中断向量PIE Vector-RAM(D00~DFFH)。

256W的中断向量PIE Vector-RAM(D00~DFFH)。

8KW的片内外设PF1、PF2(00 6000~00 7FFFH)。

8KW的片内外设PF1、PF2(00 6000~00 7FFFH)。

2KW的SARAML0(00 8000~00 87FFH)。

2KW的SARAML0(00 8000~00 87FFH)。

图2-5 28034/28035的存储器映射

1KW的DPSARAM L1(00 8800~00 8BFFH)。ECSL(Emulation Code Security Logic)指仿真代码安全逻辑。DPSARAM指双端口(Dual Port,DP)配置的SARAM。

1KW的DPSARAM L1(00 8800~00 8BFFH)。ECSL(Emulation Code Security Logic)指仿真代码安全逻辑。DPSARAM指双端口(Dual Port,DP)配置的SARAM。

1KW的DPSARAM L2(00 8C00~00 8FFFH)。

1KW的DPSARAM L2(00 8C00~00 8FFFH)。

4KW的DPSARAM L3(00 9000~00 9FFFH)。器件包含多达8K×16位的单访问RAM(L0~L3),它们被同时映射到程序与数据空间。L0块大小为2K。L1和L2块的大小都为1K,与CLA共享,可用于CLA的数据空间。L3块的大小为4K,与CLA共享,可用于CLA的程序空间。

4KW的DPSARAM L3(00 9000~00 9FFFH)。器件包含多达8K×16位的单访问RAM(L0~L3),它们被同时映射到程序与数据空间。L0块大小为2K。L1和L2块的大小都为1K,与CLA共享,可用于CLA的数据空间。L3块的大小为4K,与CLA共享,可用于CLA的程序空间。

1KW的OTP(3D 7800~3D 7BFFH)。

1KW的OTP(3D 7800~3D 7BFFH)。

64KW的Flash(3E 8000~3F 7FFFH)。

64KW的Flash(3E 8000~3F 7FFFH)。

2KW的SARAM L0(3F 8000~3F 87FFH):镜像地址,即L0存储器块既可以在高地址又可以在低地址访问。

2KW的SARAM L0(3F 8000~3F 87FFH):镜像地址,即L0存储器块既可以在高地址又可以在低地址访问。

8KW的Boot ROM(3F E000~3F FFFFH)即引导ROM。

8KW的Boot ROM(3F E000~3F FFFFH)即引导ROM。

典型的应用系统由一个28035 DSP芯片加上相应的电源、时钟、复位、JTAG电路及应用电路构成单片系统方案(Single Chip Solution)。在程序调试过程中,可以先将程序放入到片内RAM中运行仿真调试。调试完成后,再将程序放入Flash存储器中运行。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。