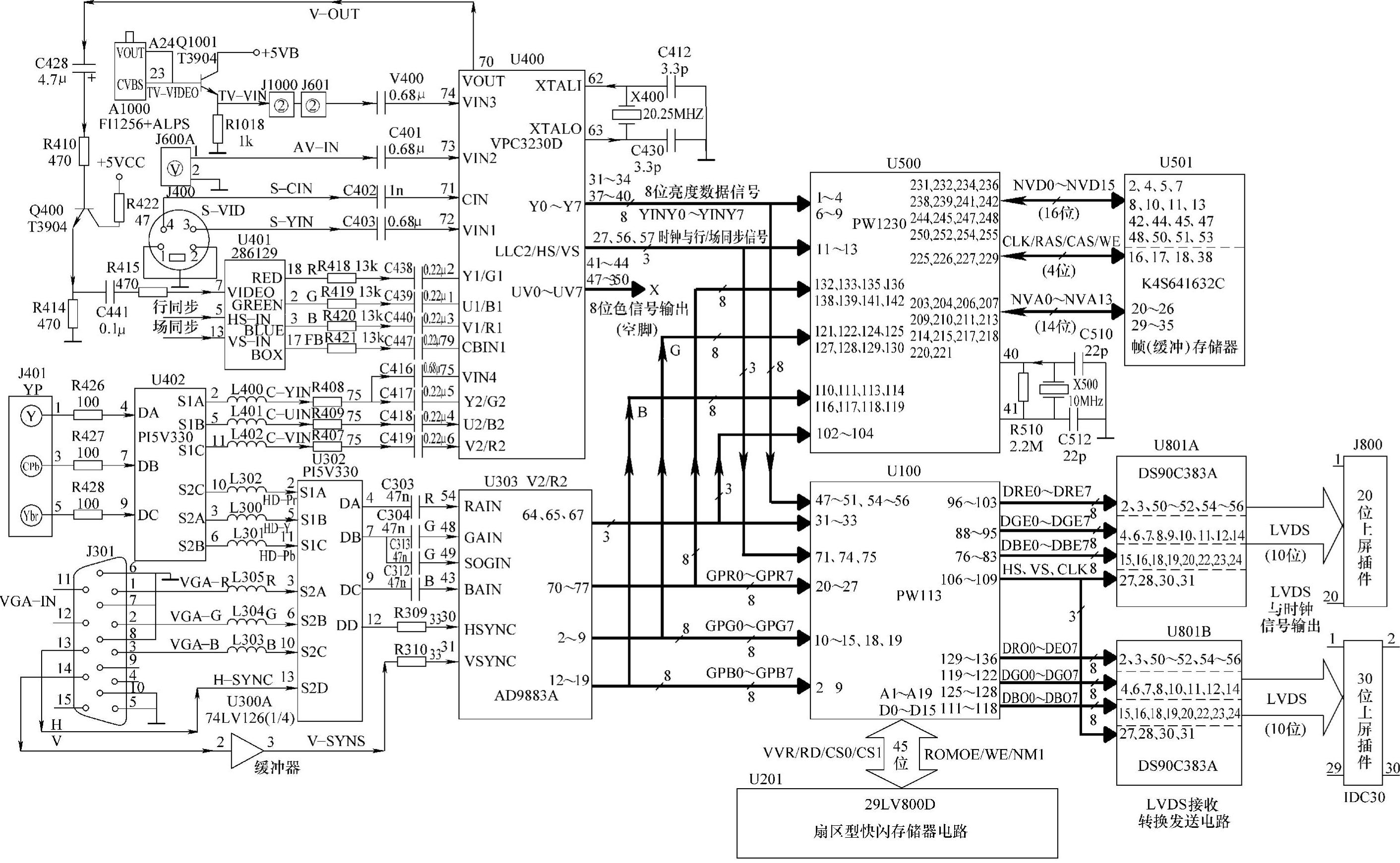

(见图4-27)

在TV状态下,由高频调谐器接收的射频信号经A1000(FI1256+ALPS)一体化高频头经高、中频处理过程处理后,分别从A1000的 脚或(23)脚输出图像中频信号至Q1001(T3904)的基极,Q1001为预中放管,经放大后的信号由发射极输出,经接插件J1000/J601的②脚,将信号送到主板电路,然后经耦合电容C400(0.68μF)将TV图像信号送入U400(VPC3230D)的(74)脚的内部电路。VPC3230D是一块亮色分离/彩色解码/A-D转换电路,内部电路的主要功能有模拟信号前端接收处理、AGC、2XADC电路;自适应型梳状滤波器NTSC/RAL制电路;NTSC/PAL/SECAM制彩色解码器、色调、色饱和度解调;视频信号混合器2D标度器和PIP全景模拟对比度、亮度峰化;输出格式器ITU-R、656/601、存储器控制;模拟分量前端4XDAC;矩阵、对比度、饱和度、亮度、色度处理电路;时钟产生(20.25MHz)和I2C总线控制;同步和时钟产生电路等。

脚或(23)脚输出图像中频信号至Q1001(T3904)的基极,Q1001为预中放管,经放大后的信号由发射极输出,经接插件J1000/J601的②脚,将信号送到主板电路,然后经耦合电容C400(0.68μF)将TV图像信号送入U400(VPC3230D)的(74)脚的内部电路。VPC3230D是一块亮色分离/彩色解码/A-D转换电路,内部电路的主要功能有模拟信号前端接收处理、AGC、2XADC电路;自适应型梳状滤波器NTSC/RAL制电路;NTSC/PAL/SECAM制彩色解码器、色调、色饱和度解调;视频信号混合器2D标度器和PIP全景模拟对比度、亮度峰化;输出格式器ITU-R、656/601、存储器控制;模拟分量前端4XDAC;矩阵、对比度、饱和度、亮度、色度处理电路;时钟产生(20.25MHz)和I2C总线控制;同步和时钟产生电路等。

图4-27 模/数视频信号处理流程示意图解

图像中频信号送入U400后,首先将信号送入模拟前端信号处理电路,经一系列处理过程后从(70)脚输出视频信号,该信号经C428(4.7μF)、R410(470Ω)送到Q400(T3904)的基极,经放大后从发射极输出,并经耦合电容C441(0.1μF)和R415(470Ω)送至模拟视频彩色处理电路U401(Z86129)的⑦脚,其主要功能和作用是将VPC3230D的(70)脚送入的模拟视频信号转换为模拟的R、G、B信号,并在行、场同步信号和I2C总线的控制下分别从(18)、②、③脚输出V-RED、V-GRN、V-BLU信号,并使以上信号经C438、C439、C440三个耦合电容回送到U400(VPC3230D)的②、①、③脚(输入端)。由U401的(17)脚输至U400的(79)脚的信号为消隐脉冲。U400的②、①、③脚内部仍为模拟电路前端信号处理电路,该信号在其内部经前端模拟处理后送入自适应梳状滤波器,经滤波处理后再进入彩色解码器、色调和色饱和度等电路进行解调。解调后的YCrCb信号送到混合处理器电路,在该电路处理过程中,受控于I2C总线的调整和时钟信的制约。混合后输出的仍为YCrCb信号,该信号被送入全景峰化处理电路作峰化处理后,进入格式器变化格式后从U400的(31)~(34)、(37)~(40)脚输出8位亮度数据信号(Y0~Y7)或视频数字图像信号,该信号被同时送到视频数字化处理与格式变换电路U500(PW1230)的①~④、⑥~⑨脚和数字视频处理与微控制信号电路U100(PW113)的(47)~(51)、(54)~(56)脚。由于以上信号的传输与处理始终要受制于时钟信号和行、场同步信号,所以经U400处理后的时钟信号和行、场同步信号也从U400的(27)、(56)、(57)脚输出,并同步送入U500、U100的相应输入端口((11)~(13)脚和(71)、(74)、(75)脚)。

以上数字信号在U500、U100两块主要芯片中的处理是一个极其复杂的过程,对于我们只顾及维修的人员而言,没有必要进行过细的剖析和计算。但有几个重点问题是必须要了解的:一是以上信号要进行正常的处理过程,必须保证有正常的工作电压供给;二是必须保证有正常的I2C总线控制电压控制;三是U100与扇区型块内存储器U201(29LV800D)和U500(PW1230)与帧(缓冲)存储器U501(K4S641632C)之间的数据通信信号电压数据必须是正常而稳定的;四是U100、U500本身的时钟振荡产生电路和复位控制电压是正常而准确的。以上四点是保证U100、U500正常工作的前提条件。

经数字化处理芯片U100、U500处理后的数字视频信号不能直接作为上屏信号,于是便从U100(PW113)的(96)~(103)脚输出8位红基色像素数据流信号;(88)~(95)脚输出8位绿基色像素数据流信号;(76)~(83)脚输出8位蓝基色像素数据流信号。这些信号分别被送到U801A(DS90C383A)的②、③、(50)~(52)、(54)~(56)脚,④、⑥、⑦、⑧、⑩、(11)、(12)、(14)脚,(15)、(16)、(18)、(19)、(20)、(22)、(23)、(24)脚。同时从PW113(U100)的(129)~(136)脚输出红基色像素数据流信号;(119)~(122)、(125)~(128)脚输出绿基色像素数据流信号;(111)~(118)脚输出蓝基色像素数据流信号。这些信号分别被送到U8018(DS90C383A)的②、③、(50)~(52)、(54)~(56)脚;④、⑥、⑦、⑧、⑩、(11)、(12)、(14)脚,(15)、(16)、(18)、(19)、(20)、(22)、(23)、(24)脚。为保证以上数据信号的正常处理,从PW113的(106)~(109)脚输出的行、场同步信号与时钟等也同时送到U801A/B的相应引脚。(https://www.daowen.com)

U801A/B是两块LVDS(低压差分信号)的接收与发送器电路,它们的主要任务和作用是将PW113进行格式变换后的24bit基色像素数据信号接收下来,经DS90C383处理变换成LVDS,送至液晶屏内部LVDS接收器(DS90C394),接收器将接收到的信号解调为原本的并行的像素数据信号。

PW113为什么不能直接将数字信号送到液晶屏?而是通过DS90C383A变成LVDS送出呢?其主要原因在4.2.12节单元电路解析中已作了详细介绍。本节不再赘述。

经DSC90C383A处理并变换后的LVDS,分别从其(47)、(48)脚,(45)、(46)脚,(41)、(42)脚,(37)、(38)脚,(39)、(40)脚输出,按5对10位经接插上屏。在其他相关电路的配合下,显示图像。

在AV状态和S端子输入的S-CIN、S-YIN信号及从(75)脚输入的视频信号,在U400(VPC3230D)内部的处理与传输过程和TV状态相同。

在视频色差端子输入视频信号状态下,在前端信号输入的方式与TV状态不同。即从J401端口输入的视频色差信号通常也称之为分量色差信号。当输入的信号分别从U402(PI5V330)的④、⑦、⑨脚输入后,经其内部开关选择后输出的为YUV信号,则分别从U402的②、⑤、(11)脚输出,分别经各自的R407、C419,R408、C417和R409、C418送至U400的⑥、⑤、④脚(输入端),进入其内部的模拟分量前端4XDAC电路,经处理后的Y/G、U/B、V/R和FB信号进入矩阵电路以及对比度、饱和度和亮/色度处理电路,经处理后变为Y、Cr、Cb/FB信号后,再送到图像混合处理电路进行混合处理,之后的图像视频信号的处理过程与TV状态相同。

若经开关选择电路U402(PI5V330)选择,输出的信号为YPbPr信号,则从U402的③、⑥、(10)脚输出。该信号分别被加到开关选择电路U302(PI5V330)的②、⑤、(11)脚,与从③、⑥、(10)脚输入的VGA信号进行选择,但不管选择哪种输入方式,最终均从④、⑦、⑨脚输出R、G、B信号送入U303(AD9883A)的(54)、(48)、(49)、(43)脚,其中从(49)脚输入的为绿色同步信号。送入AD9883A(U303)内部的R、G、B信号均为模拟信号,我们知道AD9883A是一块A-D转换电路,其主要作用就是对输入的视频图像进行A-D转换,使之变为数字信号,以方便后续电路处理。经AD9883A转换后,从(70)~(77)脚输出8位红基色像素数据流,分别送入PW113(U100)的(20)~(27)脚和PW1230(U500)的(132)、(133)、(135)、(136)、(138)、(139)、(141)、(142)脚;从②~⑨脚输出绿基色像素数据流,分别送入PW113和(10)~(15)、(18)、(17)脚和PW1230的(121)、(122)、(124)、(125)、(127)、(128)、(129)、(130)脚;从(12)~(19)脚输出蓝基色像素数据流,分别送入PW113的②~⑨脚和PW1230的(110)、(111)、(113)、(114)、(116)、(117)、(118)、(119)脚。进入U100和U500内部的数字信号处理过程和TV状态信号的处理过程完全相同。

当采用PC(个人计算机)输入VGA信号时,其VGA状态下的R、G、B信号分别输入至开关选择电路的③、⑥、⑩脚。同时行、场同步信号从VGA接口的(13)、(14)脚输出,其中行同步信号经转换开关U302的(13)脚输入,选择后从(12)脚输出,送至A-D转换电路AD9883A的(30)脚。场同步信号从(14)脚加到缓冲器U300A的②脚,经缓冲放大后送至AD9883A的(31)脚。该行、场同步信号一直被作为后续电路处理的同步脉冲信号。VGA信号的信号处理、后续流程与其他视频信号的处理相同。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。