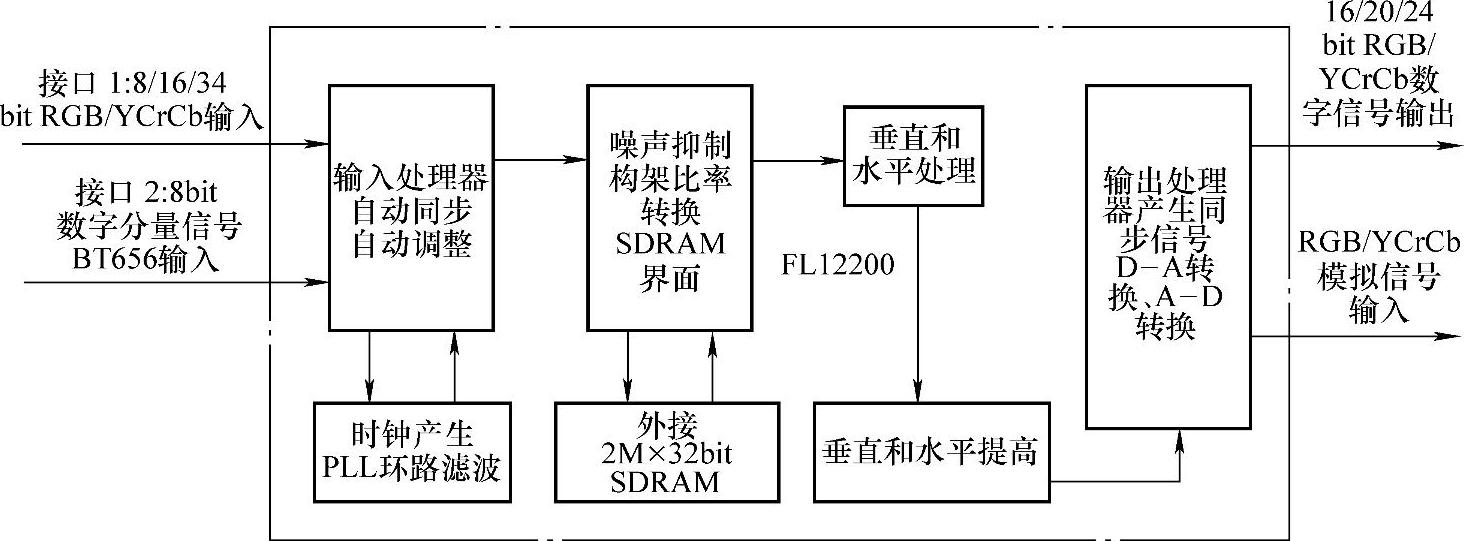

FLI2200是数字视频去隔行处理芯片,也是平板彩电常用的主要集成电路之一。它内含多种画质改善处理功能,可支持525行60Hz的NTSC制或625行50Hz的PAL/SECAM制的输入信号,可自动检测输入信号的制式,支持多种逐行输出数据格式(8/10/16/20位YUV或24/30位YPbPr/RGBHV),内含SDRAM控制器(可在外部连接2M×32bit SDRAM),内置两个I2C总线接口、时钟信号发生器及显示时序发生器等多种功能部件。

FLI2200在从复合视频信号输入到产生高质量的图像输出信号过程中,起到了非常大而且是决定性的作用——去隔行处理。FLI2200内部处理为10位/通道,输入和输出都是10位/通道,同时也支持灵敏度要求较低的8位/通道。FLI2200最低需要4MB的SDRAM才能达到或实现最高质量效果,但它也可以在牺牲灵敏度、无内存的优化模式下工作,所以它可以兼顾高端和低端产品的设计要求。

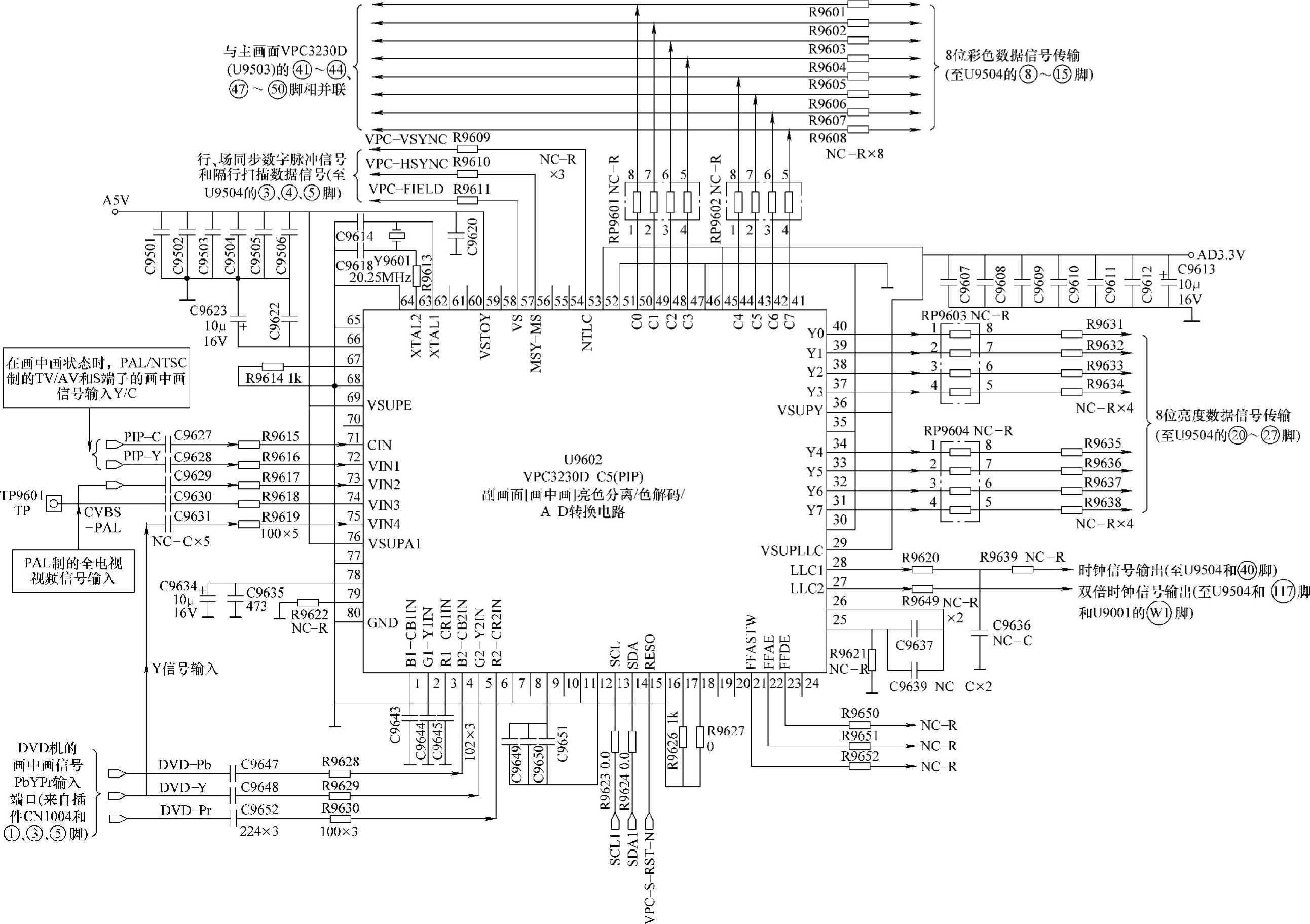

图2-7 VPC3230D-C5的应用电路解析与维修(二)

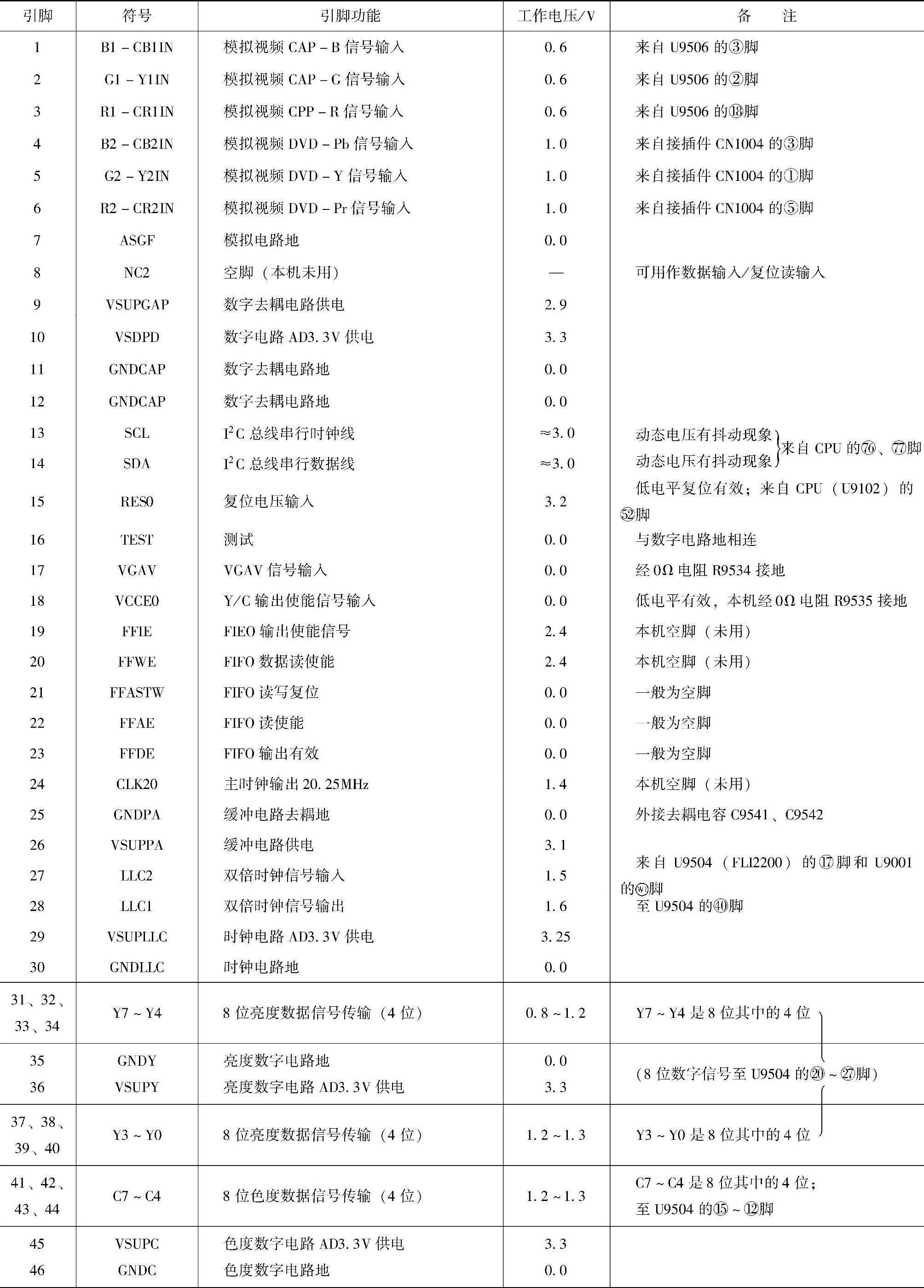

表2-5 VPC3230D-C5引脚功能及电压数据

(续)

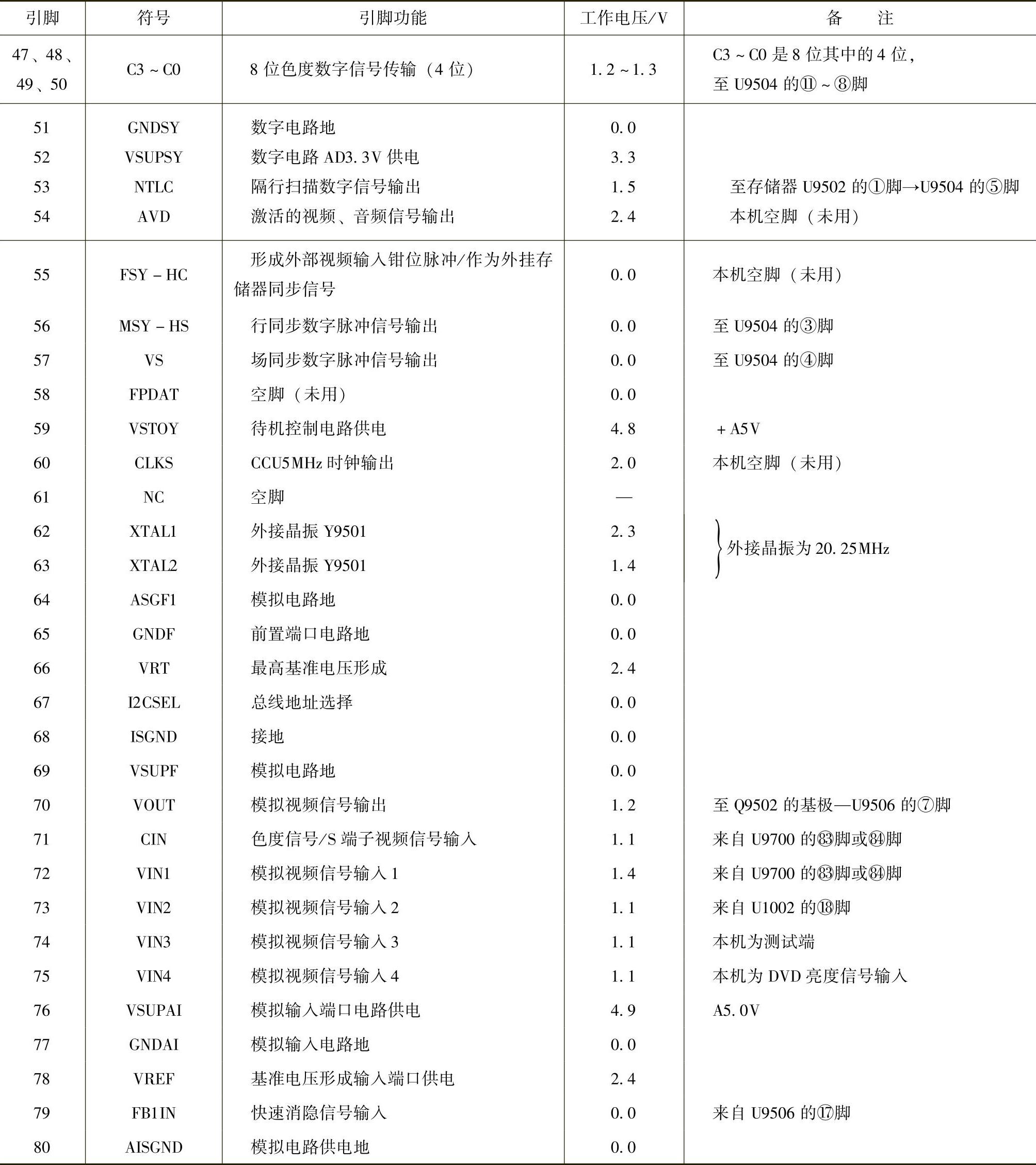

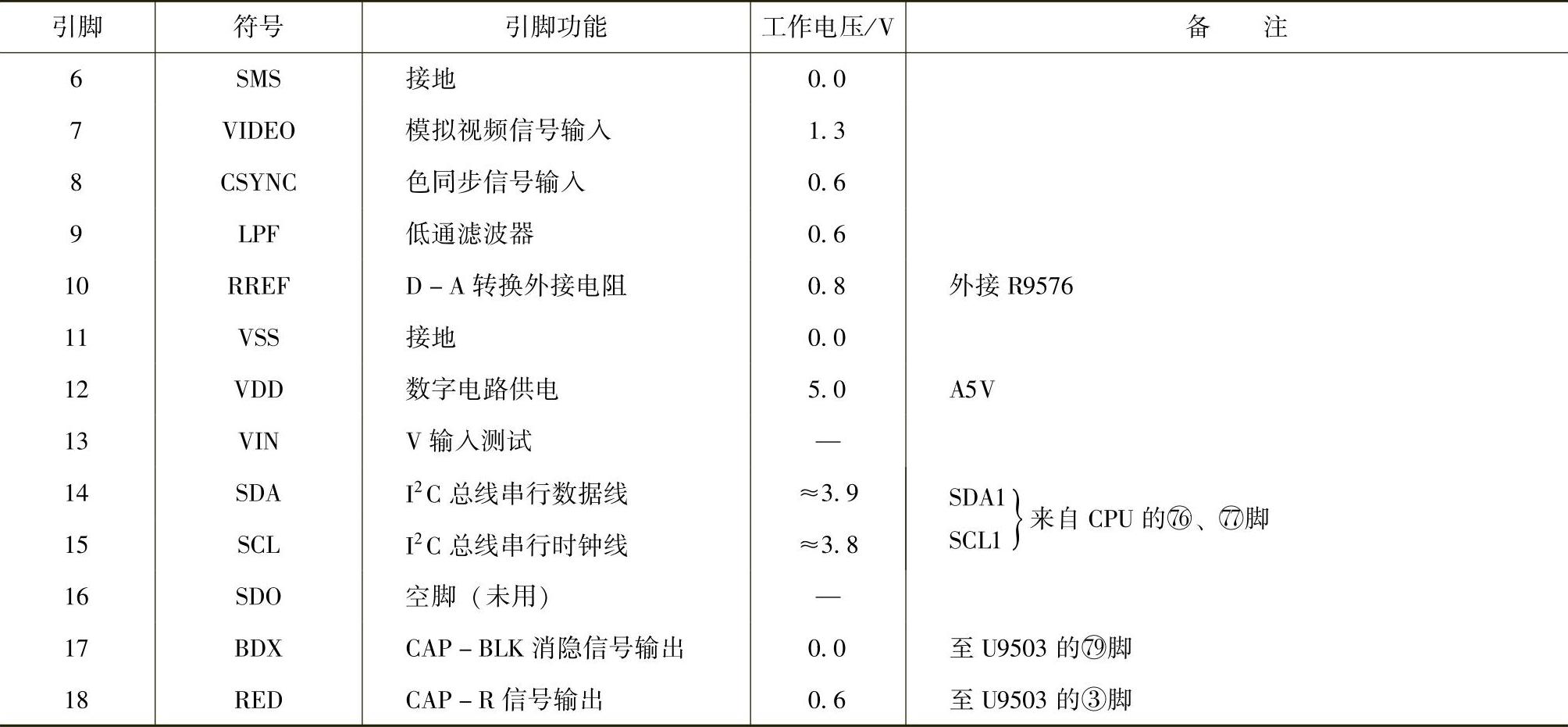

表2-6 Z8612912SSC引脚功能与电压数据

(续)

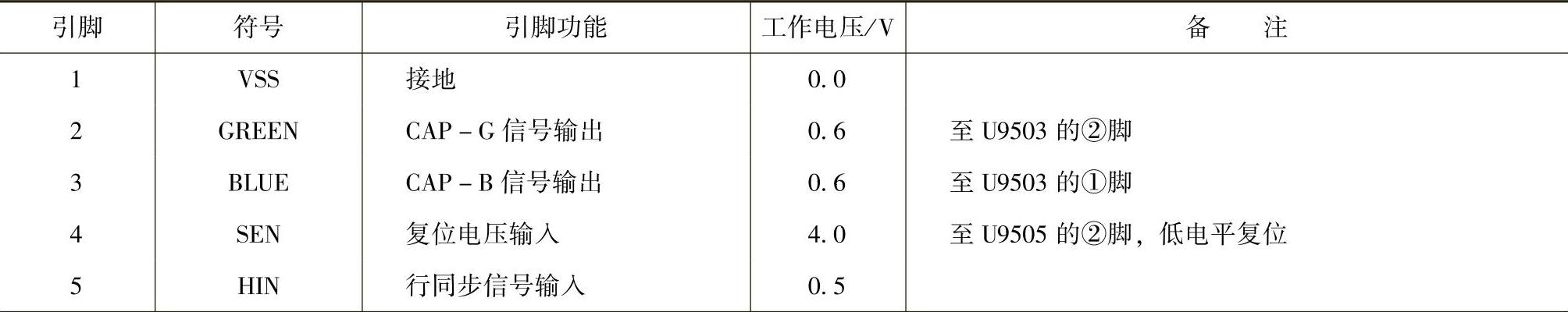

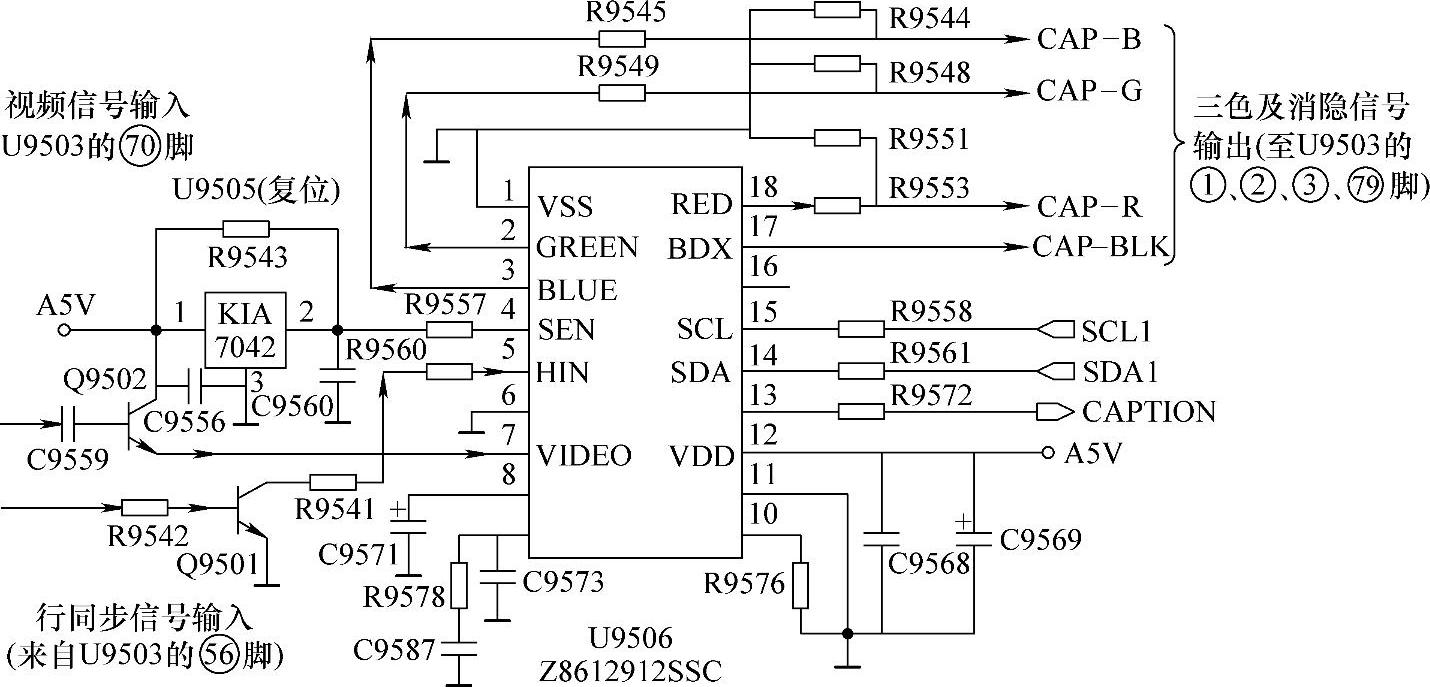

图2-8 Z8612912SSC应用电路解析与维修图解

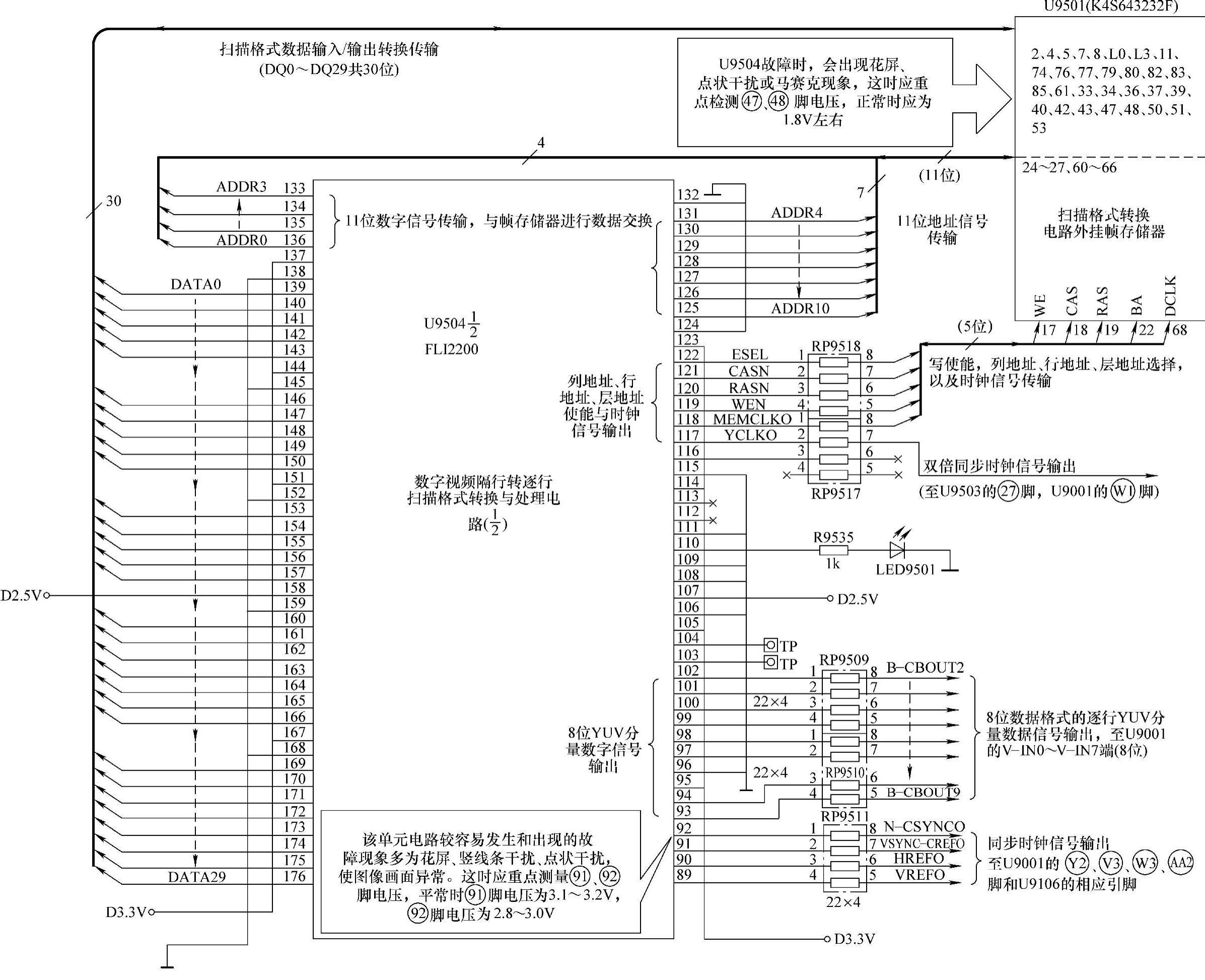

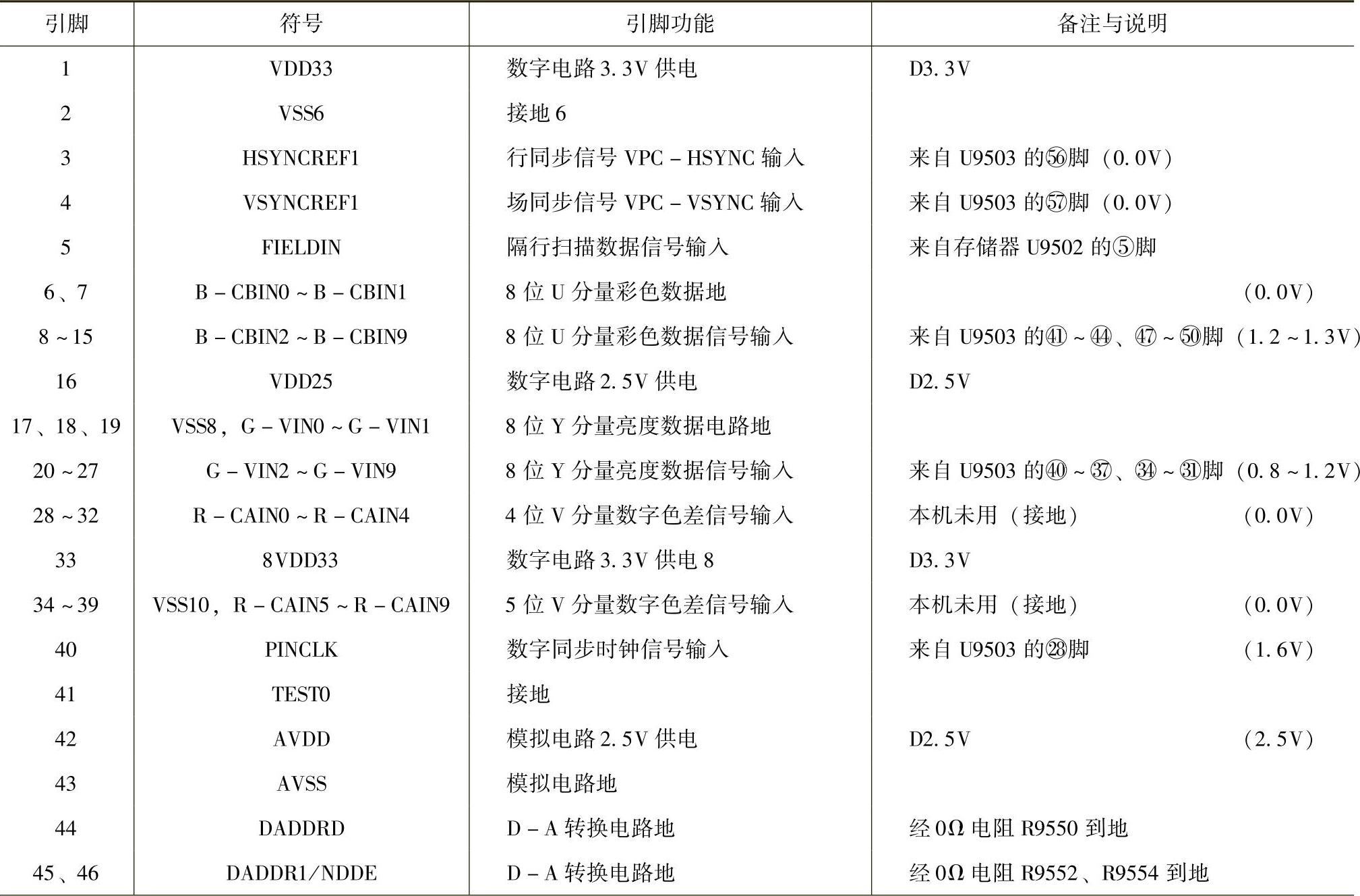

FLI2200是一种较新型的扫描格式转换电路,它集成了很多功能,可以在低耦配置时提供最大缓冲,其内置片内时钟发生器、SDRAM控制器、显示控制器、输入/输出转换器。它采用标准的二线制串行总线,更容易控制、操作寄存器。FLI2200采用172脚方形封装形式,其内部组成框图见图2-9;应用电路解析与维修图解见图2-10和图2-11。

(https://www.daowen.com)

(https://www.daowen.com)

图2-9 FLI2200内部组成框图

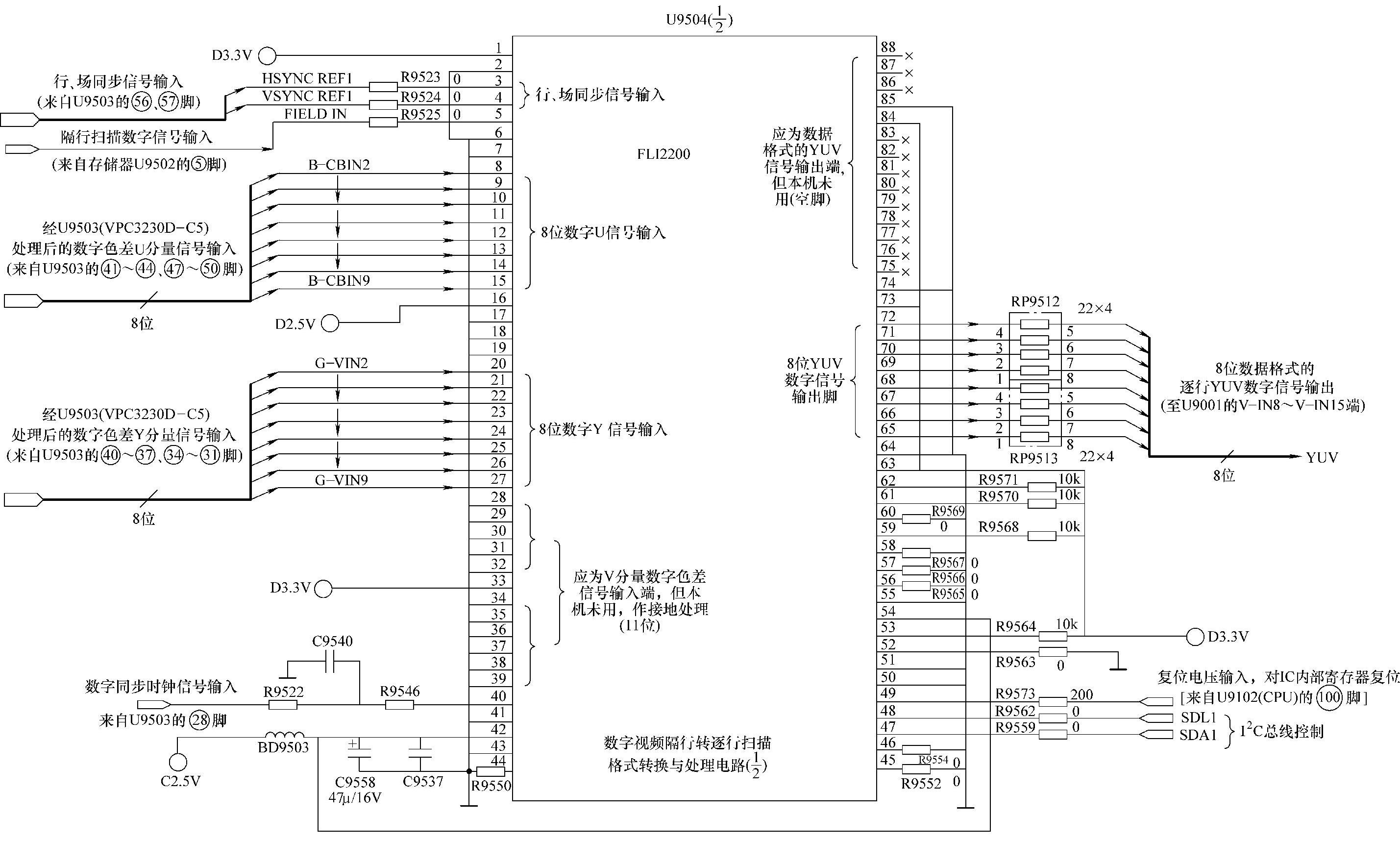

图2-10 FLI2200应用电路解析与维修图解(一)

图2-11 FLI2200应用电路解析与维修图解(二)

FLI2200工作情况解析:

经由U9503(VPC3230D-C5)分离/解码/A-D转换处理后的数字色差信号(数字格式信号)YUV分别送至FLI2200(U9504)的⑧~(15)脚和(20)~(27)脚,其中U分量的8位彩色数据信号送入U9504的⑧~(15)脚,即从VPC-CB0~VPC-CB7端送至B-CBIN2~B-CBIN9端;其中的Y分量8位亮度数据信号送入U9504的(20)~(27)脚,即从VPC-Y0~VPC-Y7端送至G-VIN2~G-VIN9端;本机V分量的输入端口未用,所以(28)~(32)脚、(34)~(39)脚均作接地处理。U9503输出的数字同步时钟信号送至U9504的(40)脚。行、场同步信号送入U9504的③、④脚,即从VPC-HSYNC、VPC-VSYNC端送入HSYNCREF1和VSYN-CREF1端。(49)脚为复位端,复位信号电压由CPU U9102(R8820LV)的(100)脚提供。以上信号的相关运作受控于(47)、(48)脚I2C总线,在I2C总线的控制下运行。经U9504内部逐行转换、画质改善、运动补偿及边缘平滑等复杂处理过程后,从U9504的(65)~(72)脚输出8位数字格式的逐行YUV数字信号至U9001的V-IN8~V-IN15端;同时从U9504的(102)~(97)、(94)、(93)脚输出8位数据格式的YUV分量数字信号至U9001的V-IN0~V-IN7端。本机的(77)~(83)、(86)、(87)、(88)脚未用而为空脚。U9504的(89)~(92)、(117)脚输出相对应的各种同步时钟信号,分别至U9001的 、

、 、

、 、

、 脚及U9503的(27)脚。以上(65)~(72)、(102)~(97)、(94)、(93)脚输出的16位YUV数字信号进入U9001进行处理。在逐行处理过程中,为了实现不同的逐行显示格式,FLI2200内部通过SDRAM接口与外挂的帧存储器U9501(K4S643232F)不断进行数据交换。获得所需的逐行显示格式从V-IN8~V-IN15和V-IN0~V-IN7端输出到U9001。

脚及U9503的(27)脚。以上(65)~(72)、(102)~(97)、(94)、(93)脚输出的16位YUV数字信号进入U9001进行处理。在逐行处理过程中,为了实现不同的逐行显示格式,FLI2200内部通过SDRAM接口与外挂的帧存储器U9501(K4S643232F)不断进行数据交换。获得所需的逐行显示格式从V-IN8~V-IN15和V-IN0~V-IN7端输出到U9001。

该单元电路较易发生的故障现象是:花屏、有竖线干扰、有点状干扰或雨点状干扰等图像问题。这时应重点检测U9504的(47)、(48)脚总线控制电压是否正常;(50)脚复位电压是否异常。并注意检测③、④脚和(92)、(91)脚行、场同步电压及帧存储器U9501的(47)、(48)脚电压,正常情况下U9504的(92)脚电压应为2.8~3.0V;(91)脚电压应为3.1~3.2V。U9501的(47)、(48)脚正常时应为稳定的1.8V。U9504的(47)、(48)脚电压应在4.0V左右微微波动。

FLI2200引脚功能及重点电压数据见表2-7。

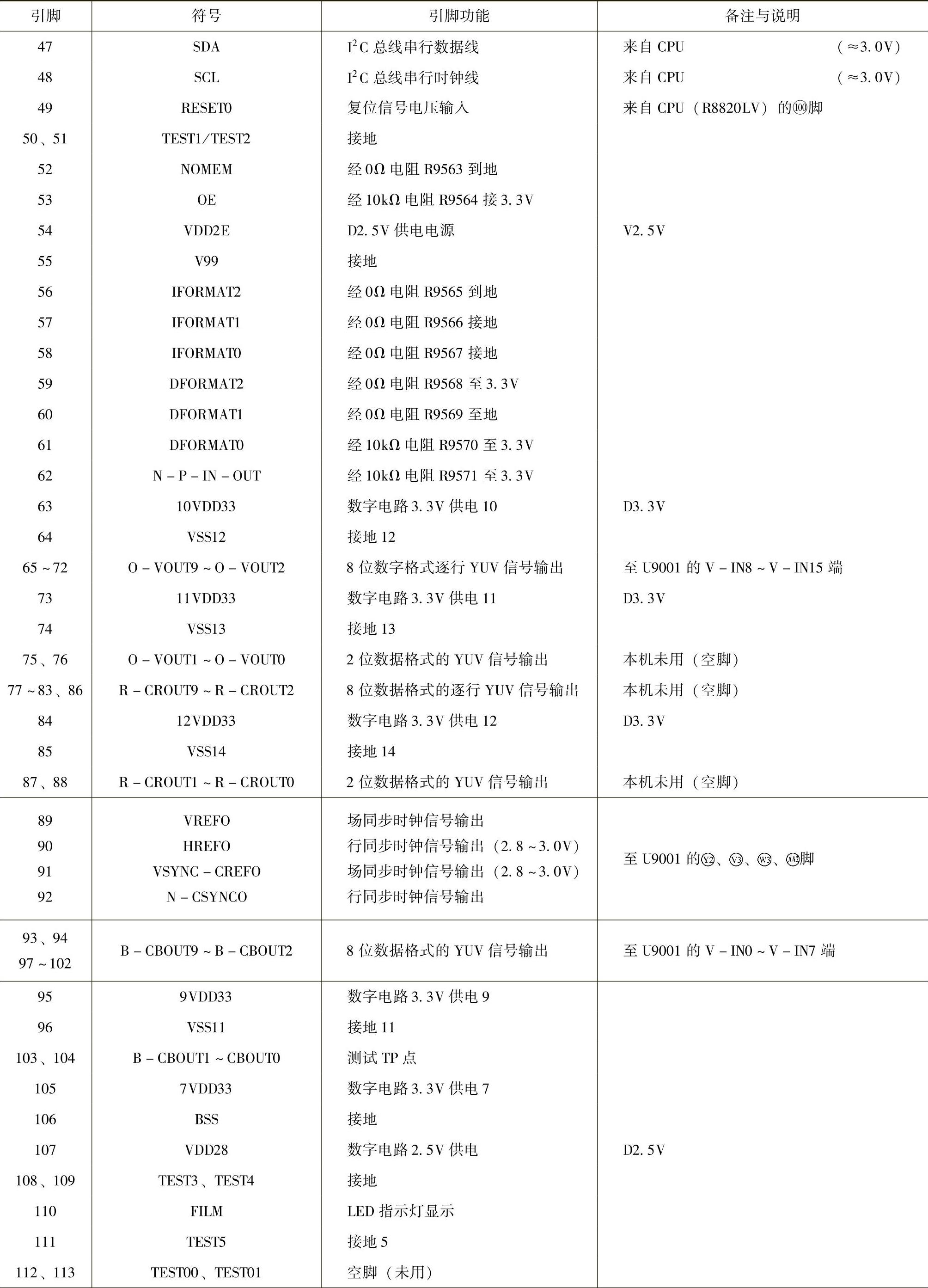

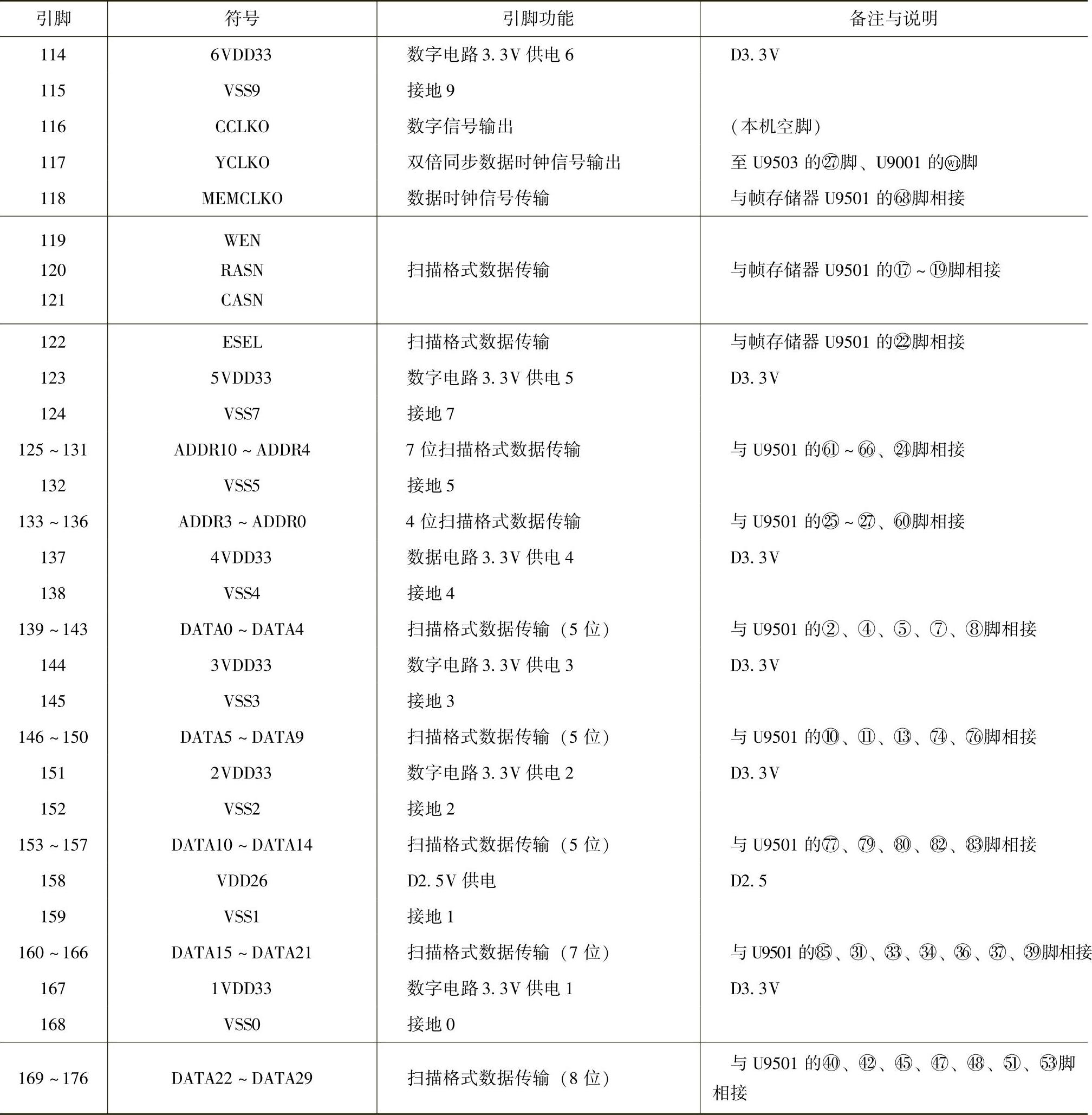

表2-7 FLI2200引脚功能及重点电压数据

(续)

(续)

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。