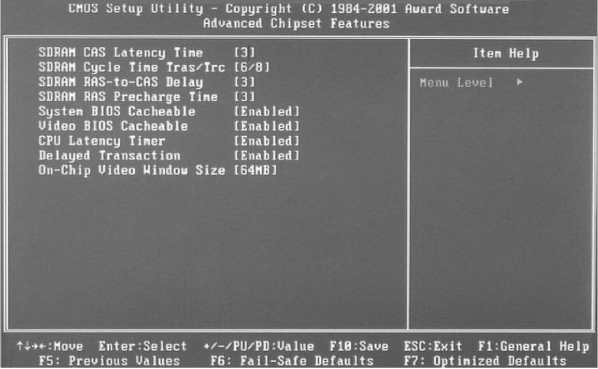

在主菜单中用方向键选择“Advanced Chipset Features”项然后回车,即进入了“Advanced Chipset Features”项子菜单,如图2-5。

图2-5

“Advanced BIOS Features”项子菜单中共有9个子项:

1.SDRAM CAS Latency Time(CAS延时周期)

此项控制内存接收到一条数据读取指令后要等待多少个时钟周期才实际执行该指令。同时该参数也决定了在一次内存突发传送过程中完成第一部分传送所需要的时钟周期数。这个参数越小,则内存的速度越快。在133MHZ频率下,品质一般的兼容内存大多只能在CAS=3下运行,在CAS=2下运行会使系统不稳定、丢失数据甚至无法启动。

2.SDRAM Cycle Time Tras/Trc(内存存取周期时钟)

该参数用于确定内存行激活时间和行周期时间的时钟周期数。Tras代表行激活时间,它是进行数据传输而开启行单元所需要的时钟周期数;Trc代表行周期时间,它是包括行单元开启和行单元刷新在内的整个过程所需要的时钟周期数。出于最佳性能考虑可将该参数设为5/7,这时内存的速度较快,但品质一般的兼容内存有可能出现因行单元开启时间不足而影响数据传输的情况。

3.SDRAM RAS-to-CAS Delay(从CAS脉冲信号到RAS脉冲信号之间延迟的时钟周期数设置)

此项允许您设定在向DRAM写入,读出或刷新时,从CAS脉冲信号到RAS脉冲信号之间延迟的时钟周期数。更快的速度可以增进系统的性能表现,而相对较慢的速度可以提供更稳定的系统表现。此项仅在系统中安装有同步DRAM时才有效。设定值:3和2(clocks)。

4.SDRAM RAS Precharge Time(RAS 预充电)(www.daowen.com)

此项用来控制RAS(Row Address Strobe)预充电过程的时钟周期数。如果在DRAM刷新前没有足够的时间给RAS积累电量,刷新过程可能无法完成而且DRAM将不能保持数据。此项仅在系统中安装了同步DRAM时才有效。

5.System BIOS Cacheable(系统缓存BIOS的容量)

该项是指经过二级缓存把系统BIOS从ROM中映射到主内存F0000h-FFFFFh,它能加快存取系统BIOS的速度,不过,操作系统很少请求BIOS,Enabled难以影响总体性能。另外,许多程序都通过这个地址来写入数据,因此一般设置为Disabled,释放内存空间并减低冲突概率。

6.Vido BIOS Cacheable(显卡BIOS的缓存容量)

该项是指经过二级缓存把视频BIOS从ROM中映射到主内存C0000h-C7FFFh,它能加快存取视频BIOS的速度,不过,操作系统很少请求视频BIOS,因此一般设置为Disabled,释放内存空间并减低冲突概率。

7.CPU Lateny Time(CPU延时时间设定)

此项控制CPU在接受了命令后是否延时执行。

8.Delayed Transaction(延迟传输)

芯片组内置了一个32-bit写缓存,可支持延迟处理时钟周期,所以在ISA总线的数据交换可以被缓存,而PCI总线可以在ISA总线数据处理的同时进行其他的数据处理。若设置为Enabled可兼容PCI 2.1规格。设定值:Enabled,Disabled。

9.On-Chip Vido Windows Size(显存容量)

显卡缓存增大可改善画面质量,但以减少可用物理内存为代价。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。